ISL6545ACRZ Intersil, ISL6545ACRZ Datasheet - Page 9

ISL6545ACRZ

Manufacturer Part Number

ISL6545ACRZ

Description

IC PWM BUCK BST VM 10DFN

Manufacturer

Intersil

Datasheet

1.ISL6545ACBZ-T.pdf

(16 pages)

Specifications of ISL6545ACRZ

Pwm Type

Voltage Mode

Number Of Outputs

1

Frequency - Max

660kHz

Duty Cycle

100%

Voltage - Supply

4.5 V ~ 14.4 V

Buck

Yes

Boost

Yes

Flyback

No

Inverting

No

Doubler

No

Divider

No

Cuk

No

Isolated

No

Operating Temperature

0°C ~ 70°C

Package / Case

10-DFN

Frequency-max

660kHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Application” on page 3 for more detail; R

resistor; R

The recommended value for R

accuracy) and then R

equation below. Since R

(see “Feedback Compensation” on page 10), it is often

easier to change R

that way the compensation calculations do not need to be

repeated. If V

Output voltages less than 0.6V are not available as shown in

Equation 2.

Input Voltage Considerations

The Typical Application diagram on page 3 shows a

standard configuration where V

12V (±20%); in each case, the gate drivers use the V

voltage for LGATE and BOOT/UGATE. In addition, V

allowed to work anywhere from 6.5V up to the 14.4V

maximum. The V

allowed for long-term reliability reasons, but transitions

through it to voltages above 6.5V are acceptable.

There is an internal 5V regulator for bias; it turns on between

5.5V and 6.5V; some of the delay after POR is there to allow

a typical power supply to ramp up past 6.5V before the

soft-start ramps begins. This prevents a disturbance on the

output, due to the internal regulator turning on or off. If the

transition is slow (not a step change), the disturbance should

be minimal. So while the recommendation is to not have the

output enabled during the transition through this region, it

may be acceptable. The user should monitor the output for

their application, to see if there is any problem.

The V

as V

sources, such as outputs of other regulators. If V

up first, and the V

initialization is done, then the soft-start will not be able to

ramp the output, and the output will later follow part of the

V

change the sequencing of the supplies, or use the

COMP/SD pin to disable V

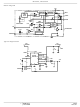

Figure 6 shows a simple sequencer for this situation. If V

powers up first, Q

Q

on, the resistor divider R

on, which will turn off Q

powers up first, Q

ISL6545x will start-up as soon as V

V

NFET’s or NPN’s or even some logic IC’s can be used as Q

or Q

V

R

IN

DISABLE

OUT

O

2

on, keeping the ISL6545x in shut-down. When V

=

ramp when it is applied. If this is not desired, then

2

CC

; but Q

=

IN

----------------------------------

V

, but can also run off a separate supply or other

R

OUT

0.6V

to the upper MOSFET can share the same supply

S

OFFSET

trip point is 0.4V nominal, so a wide variety of

•

0.6V

–

2

•

OUT

0.6V

must be low leakage when off (open-drain or

(

---------------------------

R

S

CC

R

1

IN

1

+

= 0.6V, then R

(shortened to R

OFFSET

O

will be off, and R

will be on, turning Q

R

is not present by the time the

range between 5.5V and 6.5V is NOT

O

OFFSET

)

2

S

1

, and release the shut-down. If V

and R

is part of the compensation circuit

OUT

to change the output voltage;

9

is chosen according to the

S

CC

until both supplies are ready.

2

is 1kΩ to 5kΩ (±1% for

OFFSET

determines when Q

O

is either 5V (±10%) or

CC

3

below) is the lower one.

pulling to V

comes up. The

2

S

off; so the

can be left open.

is the upper

CC

CC

ISL6545, ISL6545A

IN

powers

will turn

CC

CC

1

(EQ. 2)

turns

turns

is

CC

IN

1

open-collector) so as not to interfere with the COMP output.

Q

The V

0.6V reference). It can be as high as 20V (for V

below V

voltage.

The first consideration for high V

voltage of 36V. The V

voltage - minus the diode drop), plus any ringing (or other

transients) on the BOOT pin must be less than 36V. If V

20V, that limits V

The second consideration for high V

(BOOT - V

BOOT = V

must be <24V. So based on typical circuits, a 20V maximum

V

ringing in their particular application.

Another consideration for high V

duty cycles (such as 20V in to 1.0V out, for 5% duty cycle)

require component selection compatible with that choice

(such as low r

filter). At the other extreme (for example, 20V in to 12V out),

the upper MOSFET needs to be low r

the duty cycle gets too high, it can affect the overcurrent

sample time. In all cases, the input and output capacitors

and both MOSFETs must be rated for the voltages present.

Switching Frequency

The switching frequency is either a fixed 300kHz or 600kHz,

depending on the part number chosen (ISL6545 is 300kHz;

ISL6545A is 600kHz). However, all of the other timing

mentioned (POR delay, OCP sample, soft-start, etc.) is

independent of the clock frequency, unless otherwise noted.

BOOT Refresh

In the event that the UGATE is on for an extended period of

time, the charge on the boot capacitor can start to sag,

raising the r

has a circuit that detects a long UGATE on-time (nominal

100µs), and forces the LGATE to go high for one clock cycle,

which will allow the boot capacitor some time to recharge.

Separately, the OCP circuit has an LGATE pulse stretcher

(to be sure the sample time is long enough), which can also

help refresh the boot. But if OCP is disabled (no current

IN

2

should also be placed near the COMP/SD pin.

is a good starting assumption; the user should verify the

IN

IN

range can be as low as ~1V (for V

). There are some restrictions for running high V

IN

CC

DS(ON)

+ V

) voltage; this must be less than 24V. Since

DS(ON)

FIGURE 6. SEQUENCER CIRCUIT

CC

CC

R

R

1

2

V

of the upper MOSFET. The ISL6545x

+ ringing, that reduces to (V

IN

plus ringing to 16V.

IN

lower MOSFET, and a good LC output

(as seen on PHASE) plus V

R

Q

3

1

V

CC

IN

IN

to COMP/SD

Q

2

is duty cycle. Very low

is the maximum BOOT

IN

DS(ON)

is the maximum

OUT

. In addition, if

as low as the

OUT

IN

+ ringing)

March 3, 2011

CC

just

FN6305.6

(boot

IN

IN

is