MC908AP32CFAE Freescale Semiconductor, MC908AP32CFAE Datasheet - Page 212

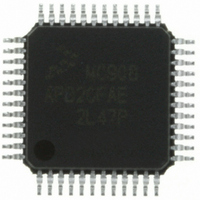

MC908AP32CFAE

Manufacturer Part Number

MC908AP32CFAE

Description

IC MCU 32K FLASH 8MHZ 48-LQFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Specifications of MC908AP32CFAE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, IRSCI, SCI, SPI

Peripherals

LED, LVD, POR, PWM

Number Of I /o

32

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

Controller Family/series

HC08

No. Of I/o's

32

Ram Memory Size

2KB

Cpu Speed

8MHz

No. Of Timers

2

Embedded Interface Type

I2C, SCI, SPI

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AP32CFAE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC908AP32CFAER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 212 of 324

- Download datasheet (4Mb)

Serial Peripheral Interface Module (SPI)

13.4 Functional Description

Figure 13-2

The SPI module allows full-duplex, synchronous, serial communication between the MCU and peripheral

devices, including other MCUs. Software can poll the SPI status flags or SPI operation can be

interrupt-driven.

The following paragraphs describe the operation of the SPI module.

13.4.1 Master Mode

The SPI operates in master mode when the SPI master bit, SPMSTR, is set.

Only a master SPI module can initiate transmissions. Software begins the transmission from a master SPI

module by writing to the transmit data register. If the shift register is empty, the byte immediately transfers

to the shift register, setting the SPI transmitter empty bit, SPTE. The byte begins shifting out on the MOSI

pin under the control of the serial clock. (See

The SPR1 and SPR0 bits control the baud rate generator and determine the speed of the shift register.

(See

master also controls the shift register of the slave peripheral.

As the byte shifts out on the MOSI pin of the master, another byte shifts in from the slave on the master’s

MISO pin. The transmission ends when the receiver full bit, SPRF, becomes set. At the same time that

SPRF becomes set, the byte from the slave transfers to the receive data register. In normal operation,

SPRF signals the end of a transmission. Software clears SPRF by reading the SPI status and control

register with SPRF set and then reading the SPI data register. Writing to the SPI data register clears the

SPTE bit.

210

$0010 SPI Control Register (SPCR)

$0011

$0012

Addr.

13.13.2 SPI Status and Control

SPI Status and Control

Register Name

shows the structure of the SPI module.

SPI Data Register

Configure the SPI modules as master or slave before enabling them.

Enable the master SPI before enabling the slave SPI. Disable the slave SPI

before disabling the master SPI. (See

(SPSCR)

Register

(SPDR)

Reset:

Reset:

Reset:

Read:

Read:

Read:

Write:

Write:

Write:

Figure 13-1. SPI I/O Register Summary

MC68HC908AP Family Data Sheet, Rev. 4

SPRIE

SPRF

Bit 7

R7

T7

0

0

Register.) Through the SPSCK pin, the baud rate generator of the

= Unimplemented

ERRIE

R6

T6

R

Figure

6

0

0

NOTE

SPMSTR

=

13-3.)

OVRF

13.13.1 SPI Control

R5

T5

5

1

0

MODF

Unaffected by reset

CPOL

R4

T4

4

0

0

CPHA

SPTE

R3

T3

R

3

1

1

Register.)

= Reserved

MODFEN

SPWOM

R2

T2

2

0

0

Freescale Semiconductor

SPR1

SPE

R1

T1

1

0

0

SPTIE

SPR0

Bit 0

R0

T0

0

0

Related parts for MC908AP32CFAE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: