MC908AP32CFAE Freescale Semiconductor, MC908AP32CFAE Datasheet - Page 294

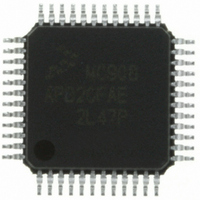

MC908AP32CFAE

Manufacturer Part Number

MC908AP32CFAE

Description

IC MCU 32K FLASH 8MHZ 48-LQFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Specifications of MC908AP32CFAE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, IRSCI, SCI, SPI

Peripherals

LED, LVD, POR, PWM

Number Of I /o

32

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

Controller Family/series

HC08

No. Of I/o's

32

Ram Memory Size

2KB

Cpu Speed

8MHz

No. Of Timers

2

Embedded Interface Type

I2C, SCI, SPI

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AP32CFAE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC908AP32CFAER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 294 of 324

- Download datasheet (4Mb)

Break Module (BRK)

The following events can cause a break interrupt to occur:

When a CPU-generated address matches the contents of the break address registers, the break interrupt

begins after the CPU completes its current instruction. A return-from-interrupt instruction (RTI) in the

break routine ends the break interrupt and returns the MCU to normal operation.

structure of the break module.

21.3.1 Flag Protection During Break Interrupts

The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during

the break state.

21.3.2 CPU During Break Interrupts

The CPU starts a break interrupt by:

The break interrupt begins after completion of the CPU instruction in progress. If the break address

register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

21.3.3 TIMI and TIM2 During Break Interrupts

A break interrupt stops the timer counters.

21.3.4 COP During Break Interrupts

The COP is disabled during a break interrupt when V

21.4 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

292

•

•

•

•

A CPU-generated address (the address in the program counter) matches the contents of the break

address registers.

Software writes a logic 1 to the BRKA bit in the break status and control register.

Loading the instruction register with the SWI instruction

Loading the program counter with $FFFC and $FFFD

($FEFC and $FEFD in monitor mode)

IAB15–IAB0

Figure 21-2. Break Module Block Diagram

IAB15–IAB8

IAB7–IAB0

MC68HC908AP Family Data Sheet, Rev. 4

BREAK ADDRESS REGISTER HIGH

BREAK ADDRESS REGISTER LOW

8-BIT COMPARATOR

8-BIT COMPARATOR

TST

is present on the RST pin.

CONTROL

Figure 21-2

BREAK

Freescale Semiconductor

shows the

Related parts for MC908AP32CFAE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: