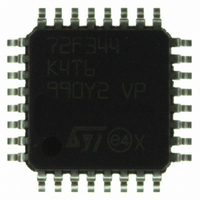

ST72F344K4T6 STMicroelectronics, ST72F344K4T6 Datasheet - Page 13

ST72F344K4T6

Manufacturer Part Number

ST72F344K4T6

Description

MCU 8BIT 16KB FLASH MEM 32-LQFP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST72F344K2T6.pdf

(247 pages)

Specifications of ST72F344K4T6

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, LIN, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

24

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

Processor Series

ST72F3x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

I2C, SCI, SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

34

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

ST72F34X-SK/RAIS, ST7MDT40-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

497-5046 - KIT TOOL FOR ST7/UPSD/STR7 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-5611

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST72F344K4T6

Manufacturer:

STMicroelectronics

Quantity:

10 000

Company:

Part Number:

ST72F344K4T6TR

Manufacturer:

STMicroelectronics

Quantity:

10 000

ST72344xx ST72345xx

Figure 48.

Figure 49.

Figure 50.

Figure 51.

Figure 52.

Figure 53.

Figure 54.

Figure 55.

Figure 56.

Figure 57.

Figure 58.

Figure 59.

Figure 60.

Figure 61.

Figure 62.

Figure 63.

Figure 64.

Figure 65.

Figure 66.

Figure 67.

Figure 68.

Figure 69.

Figure 70.

Figure 71.

Figure 72.

Figure 73.

Figure 74.

Figure 75.

Figure 76.

Figure 77.

Figure 78.

Figure 79.

Figure 80.

Figure 81.

Figure 82.

Figure 83.

Figure 84.

Figure 85.

Figure 86.

Figure 87.

Figure 88.

Figure 89.

Figure 90.

Figure 91.

Figure 92.

Figure 93.

Figure 94.

Figure 95.

Figure 96.

Figure 97.

Figure 98.

Figure 99.

Input capture timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Output compare block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Output compare timing diagram, f

Output compare timing diagram, f

One-pulse mode cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

One-pulse mode timing example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Pulse width modulation mode timing example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Pulse width modulation cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Serial peripheral interface block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Single master/ single slave application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Generic SS timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Hardware/software slave select management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Data clock timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Clearing the WCOL bit (write collision flag) software sequence . . . . . . . . . . . . . . . . . . . . 123

Single master / multiple slave configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

SCI block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Word length programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

SCI baud rate and extended prescaler block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Bit sampling in reception mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

I2C bus protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Transfer sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Event flags and interrupt generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

I2C bus protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

16-bit word write operation flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

16-bit word read operation flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Transfer sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Byte write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Page write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Current address read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Random read (dummy write + restart + current address read). . . . . . . . . . . . . . . . . . . . . 175

Random read (dummy write + stop + start + current address read) . . . . . . . . . . . . . . . . . 176

Sequential read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Combined format for read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Event flags and interrupt generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

ADC block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Pin loading conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

f

Typical RC frequency vs. RCCR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Typical I

Typical I

Typical I

Typical I

Typical I

Typical I

Typical I

Typical application with an external clock source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Typical application with a crystal or ceramic resonator . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Two typical applications with unused I/O pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Typical V

I2C interface block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

I2C3S interface block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

CPU

maximum operating frequency versus V

DD

DD

DD

DD

DD

DD

DD

OL

in Run vs. f

in Run at f

in Slow vs. f

in Wait vs. f

in Wait at f

in Slow-wait vs. f

vs. temp. at V

at V

DD

= 2.4 V (std I/Os) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

CPU

CPU

CPU

CPU

CPU

DD

= 8 MHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

= 8 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

CPU

= 5 V and f

Doc ID 12321 Rev 5

TIMER

TIMER

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

CPU

= f

= f

CPU

CPU

= 8 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

DD

/2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

/4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

supply voltage . . . . . . . . . . . . . . . . . . . 202

List of figures

13/247