LP3907QTLX-VXSS/NOPB National Semiconductor, LP3907QTLX-VXSS/NOPB Datasheet - Page 21

LP3907QTLX-VXSS/NOPB

Manufacturer Part Number

LP3907QTLX-VXSS/NOPB

Description

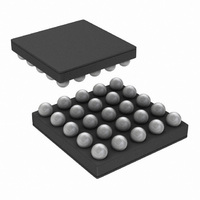

IC REG BUCK SYNC-2 LDO-2 25MSMD

Manufacturer

National Semiconductor

Series

PowerWise®r

Datasheet

1.LP3907SQ-JXQXNOPB.pdf

(46 pages)

Specifications of LP3907QTLX-VXSS/NOPB

Topology

Step-Down (Buck) Synchronous (2), Linear (LDO) (2)

Function

Any Function

Number Of Outputs

4

Frequency - Switching

2.1MHz

Voltage/current - Output 1

1.8V, 1A

Voltage/current - Output 2

3.3V, 600mA

Voltage/current - Output 3

2.8V, 300mA

W/led Driver

No

W/supervisor

No

W/sequencer

Yes

Voltage - Supply

2.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

25-UFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

tions. When the output drops below the ‘low’ PFM threshold,

the cycle repeats to restore the output voltage to ~1.6% above

the nominal PWM output voltage.

If the load current should increase during PFM mode (see

figure below) causing the output voltage to fall below the

‘low2’ PFM threshold, the part will automatically transition into

fixed-frequency PWM mode.

SW1, SW2 OPERATION

SW1 and SW2 have selectable output voltages ranging from

0.8V to 3.5V (typ.). Both SW1 and SW2 in the LP3907 are

I

internal state machine of the LP3907 following a Power-On

event that moves the operating mode to the Active state. (see

SHUTDOWN MODE

During shutdown the PFET switch, reference, control and

bias circuitry of the converters are turned off. The NFET

switch will be on in shutdown to discharge the output. When

the converter is enabled, soft start is activated. It is recom-

mended to disable the converter during the system power up

and under voltage conditions when the supply is less than

2.8V.

SOFT START

The soft-start feature allows the power converter to gradually

reach the initial steady state operating point, thus reducing

startup stresses and surges. The two LP3907 buck convert-

ers have a soft-start circuit that limits in-rush current during

startup. During startup the switch current limit is increased in

steps. Soft start is activated only if EN goes from logic low to

logic high after V

increasing switch current limit in steps of 180mA, 300mA, and

720mA for Buck1; 161mA, 300mA and 536mA for Buck2 (typ.

Switch current limit). The start-up time thereby depends on

the output capacitor and load current demanded at start-up.

2

C register controlled and are enabled by default through the

IN

reaches 2.8V. Soft start is implemented by

21

Power On Sequence). The SW1 and SW2 output voltages

revert to default values when the power on sequence has

been completed. The default output voltage for each buck

converter is factory programmable. (See Application Notes).

SW1, SW2 CONTROL REGISTERS

SW1, SW2 can be enabled/disabled through the correspond-

ing control register.

The Modulation mode PWM/PFM is by default automatic and

depends on the load as described above in the functional de-

scription. The modulation mode can be overridden by setting

I

forcing the buck to operate in PWM mode regardless of the

load condition.

LOW DROPOUT OPERATION

The LP3907 can operate at 100% duty cycle (no switching;

PMOS switch completely on) for low drop out support of the

output voltage. In this way the output voltage will be controlled

down to the lowest possible input voltage. When the device

operates near 100% duty cycle, output voltage ripple is ap-

proximately 25mV. The minimum input voltage needed to

support the output voltage is

V

— I

— R

— R

2

C bit to a logic 1 in the corresponding buck control register,

IN, MIN

LOAD

DSON, PFET

INDUCTOR

= I

LOAD

* (R

Load current

Drain to source resistance of

Inductor resistance

DSON, PFET

PFET switch in the triode region

+ R

INDUCTOR

) + V

30017814

OUT

www.national.com