EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 604

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

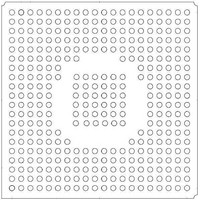

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 604 of 824

- Download datasheet (13Mb)

17

17-8

IrDA

EP93xx User’s Guide

17.3.3 Control Information Buffering

17.4.1 Introduction

17.4.1.1 Bit Encoding

17.4 Medium IrDA Specific Features

The ARM Core needs several items of information about a received frame that are not held in

data DMAed from the

may be receiving the next frame by the time the ARM Core starts to work on the frame just completed).

The additional information is as follows:

A control information buffer register is loaded whenever an end of received frame condition occurs.

This event also generates an interrupt, which must be serviced before the end of the next received

frame (at which point the buffered control information would be overwritten). The interrupt may be

cleared by reading from the control information buffer

position.

The MIR comprises a dedicated serial port and RZI modulator/demodulator supporting the

Infrared Data Association (IrDA) standard for transmission/reception at 0.576 and

1.152 Mb/s.

Frames contain an 8 bit address, an optional control field, a data field of any size that is a

multiple of 8 bits and a 16-bit CRC-CCITT. The start/stop flag and CRC generation/checking

is performed in the hardware. Data can be selectively saved in the receive buffer by

programming an address with which to compare against all incoming frames. Interrupts are

signalled when CRC checks performed on received data indicate an error, when a receiver

abort occurs, when the transmit buffer underruns during an active frame and is aborted, when

the receive buffer overruns and data is lost.

The MIR bit encoding uses an RZI modulation scheme where a “0” is represented by a light

pulse. For both 0.576 and 1.152 Mbps data rates, the optical pulse duration is normally 1/4 of

a bit duration. For example, if the data frame (in the order of transmission) is 11010010b, then

Figure 17-1

• A receive overrun or framing error occurred during frame reception.

• The frame failed the CRC check at the end of reception.

• Transmission of the frame was aborted.

•

The number of bytes of valid data received in the frame (i.e. up to the end of frame or the

overrun/framing error

represents the signal that is actually transmitted.

receive FIFO, or stored in the DMA controller itself (because the DMA unit

condition).

Copyright 2007 Cirrus Logic

register or by writing a ‘1’ to its status bit

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc