EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 661

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

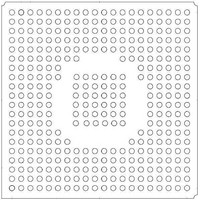

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 661 of 824

- Download datasheet (13Mb)

DS785UM1

21.3 I

The I

control registers. Once the new configuration has been set, the channels can be re-enabled

following the specified start order.

If a channel is enabled while the FIFO is empty, no samples are read from the FIFO. The I

controller will parallel load whatever is currently in the left holding register into the shift

register. Once these contents have been shifted out, the right holding register is then parallel

loaded into the shift register and then shifted out. If this occurs after the I

been reset, these holding registers will contain zero. If the I

after an earlier transmission, the holding registers will contain the last samples that were

copied into them. As before, the I

holding register has been loaded into the shift register. At this point, if the FIFO is still empty,

the I

the I

a status bit in the Global Control Status register, I2SGlSts. (See “Register Descriptions” on

page 448.) To clear the underflow the programmer must write at least one left and right stereo

sample to the FIFO. Disabling the I

The status of each FIFO is reflected in the Global Control Status register. There are 5 bits for

each FIFO in this register that reflect the state of the FIFO. They are as follows:

The I

Core to receive stereo information from external CODECS.

Each I

channel can operate in master and slave mode. Data is received from the channel input and

transferred into two registers, the left and right stereo pair. The ARM can then read the data

from the channel. The key features are shown below.

2

• Tx0_underflow - Gets set when the I

• Tx0_overflow - Gets set when the programmer attempts to write to the FIFO when it is

• Tx0_fifo_empty - Gets set when there no left and right stereo samples in the FIFO.

• Tx0_fifo_half_empty - Gets set when there are 4 left and right stereo samples or less in

• Tx0_fifo_full - Gets set when there are 8 left and right stereo samples in the FIFO.

• Three Receive data channels, master or slave mode.

• Supports 16/24/32 bit word lengths.

• Programmable left/right word clock polarity on the serial frame.

• Programmable bit clock polarity.

• Programmable data validity, that is, data valid on the rising/negative edge of the bit

S Receiver Channel Overview

2

2

full.

the FIFO.

clock.

2

2

S controller will assert the FIFO underflow flag. No attempt is made to read the FIFO by

S controller and the read pointer stays pointing to location 0. The underflow will update

S transmit and receive channels should be disabled before changes are made to the

S Receiver channel enables audio compression algorithms executing on the ARM

2

S RX channel provides a single stereo I

Copyright 2007 Cirrus Logic

2

S controller will attempt to read the FIFO after the right

2

S controller will also clear the underflow.

2

S controller reads the FIFO when it is empty.

2

S compliant input channel. The Receive

2

S controller has been re-enabled

2

S controller has

EP93xx User’s Guide

I

2

S Controller

21-5

2

S

21

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc