EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 719

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 719 of 824

- Download datasheet (13Mb)

DS785UM1

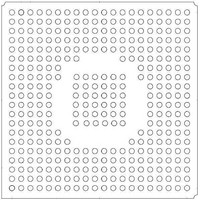

23.5.8 Motorola SPI Format with SPO=0, SPH=1

SFRMOUT /

SFRMIN

SCLKOUT /

SCLKIN

The transfer signal sequence for Motorola SPI format with SPO=0, SPH=1 is shown in

Figure

In this configuration, during idle periods:

If the SSP is enabled and there is valid data within the transmit FIFO, the start of

transmission is signified by the SFRMOUT master signal being driven LOW. The master

SSPTXD output pad is enabled. After a further one half SCLKOUT period, both master and

slave valid data is enabled onto their respective transmission lines. At the same time, the

SCLKOUT is enabled with a rising edge transition.

Data is then captured on the falling edges and propagated on the rising edges of the

SCLKOUT signal.

In the case of a single word transfer, after all bits have been transferred, the SFRMOUT line

is returned to its idle HIGH state one SCLKOUT period after the last bit has been captured.

For continuous back-to-back transfers, the SFRMOUT pin is held LOW between successive

data words and termination is the same as that of the single word transfer.

SSRXD

SSTXD

SSPOE

• the SCLKOUT signal is forced LOW

• SFRMOUT is forced HIGH

• the transmit data line SSPTXD is arbitrarily forced LOW

• when the SSP is configured as a master, the SSPCTLOE line is driven LOW, enabling

• when the SSP is configured as a slave, the SSPCTLOE line is driven HIGH, disabling

the SCLKOUT pad (active LOW enable)

the SCLKOUT pad (active LOW enable).

23-5, which covers both single and continuous transfers.

Q

Figure 23-5. Motorola SPI Frame Format with SPO=0 and SPH=1

M SB

MS B

Copyright 2007 Cirrus Logic

4 t o 16 bi t s

Synchronous Serial Port

EP93xx User’s Guide

LS B

LS B

Q

23-7

23

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc