LH79520N0M000B1 NXP Semiconductors, LH79520N0M000B1 Datasheet - Page 38

LH79520N0M000B1

Manufacturer Part Number

LH79520N0M000B1

Description

Manufacturer

NXP Semiconductors

Datasheet

1.LH79520N0M000B1.pdf

(59 pages)

Specifications of LH79520N0M000B1

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Processing Unit

Microcontroller

Operating Supply Voltage (min)

1.62V

Operating Supply Voltage (typ)

1.8V

Operating Supply Voltage (max)

1.98V

Package Type

LQFP

Screening Level

Industrial

Pin Count

176

Mounting

Surface Mount

Rad Hardened

No

Lead Free Status / RoHS Status

Not Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LH79520N0M000B1

Manufacturer:

Sharp Microelectronics

Quantity:

10 000

LH79520

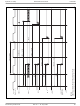

External DMA Handshake Signal Timing

DREQ TIMING

DREQ1 must not transition from LOW to HIGH again

until after nDACK0 or DACK1 has been asserted.

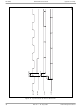

DACK/DEOT TIMING

DACK1, DEOT0 and DEOT1 occur in relation to an

external bus access to/from the external peripheral that

requested the DMA transfer.

38

NOTE: tDREQ0L = DREQ0 LOW Pulse Width = 2 HCLK MIN.

As Figure 18 shows, once asserted, DREQ0 or

These timing diagrams indicate when nDACK0,

tDREQ1L = DREQ1 LOW Pulse Width = 2 HCLK MIN.

n DACK0

DREQ0,

DREQ1

DACK1

Figure 18. DREQ Timing Restrictions

CHANGE STATE

Rev. 01 — 16 July 2007

MUST NOT

NXP Semiconductors

DREQ

TRANSITON

DREQ MAY

read or the last word of a burst read from the requesting

peripheral. Figure 20 shows the timing with relation to

a single write or the last word of a burst write to the

requesting peripheral.

able when a Write to SDRAM occurs just prior to a sin-

gle word Write to the requesting peripheral. If the write

buffer is enabled for the SDRAM Controller, this can

cause the DACK/DEOT to occur an indeterminate

number of cycles prior to the actual Write to the

requesting peripheral.

Figure 19 shows the timing with relation to a single

The timing of DACK/DEOT may become unpredict-

tDREQ0L,

tDREQ1L

Preliminary data sheet

System-on-Chip

79520-158