EP1S80B956C7N Altera, EP1S80B956C7N Datasheet - Page 660

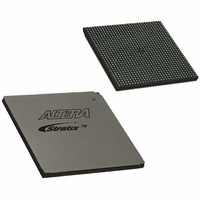

EP1S80B956C7N

Manufacturer Part Number

EP1S80B956C7N

Description

IC STRATIX FPGA 80K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S80B956C7N

Number Of Logic Elements/cells

79040

Number Of Labs/clbs

7904

Total Ram Bits

7427520

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 660 of 864

- Download datasheet (11Mb)

Interfaces

Figure 8–12. Stratix & Stratix GX XGMII Output Implementation (One Channel)

8–16

Stratix Device Handbook, Volume 2

Stratix & Stratix GX PCS Output

Logic Array

Stratix GX

Stratix &

DATA

CLK

D0,D2,D4,D6

D1,D3,D5,D7

8

PLL

Figure 8–13

From the receiver side, the DDR data is captured from the MAC to the

Stratix and Stratix GX PCS DDR input circuitry. The serial data is

separated into two individual data streams with the even bits routed to

the top register and odd bits routed to the bottom register. The DDR input

circuitry produces two output data streams that go into the shift registers.

From the shift registers, the data is deserialized using the clock from the

MAC, combining into an 8-bit word. This parallel data goes to a register

that is clocked by the divide-by-4 clock from the PLL. This data and clock

go to the Stratix and Stratix GX core. This implementation shows only one

channel, but can be duplicated to include all 32 bits of the TX_D signal and

all 4 bits of the TX_C signal.

×4

4

4

39.0625 MHz

156.25 MHz

Register

Register

Shift

Shift

DDR Output Circuitry

shows one channel of the input half of the XGMII interface.

DFF

DFF

MAC_RXCLK

156.25 MHz

312.5 Mbps

RX_D[0]

Altera Corporation

DATA

CLK

Receiver

MAC

July 2005

Related parts for EP1S80B956C7N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: