MC68LC060RC66 Freescale Semiconductor, MC68LC060RC66 Datasheet - Page 346

MC68LC060RC66

Manufacturer Part Number

MC68LC060RC66

Description

IC MPU 32BIT 66MHZ 206-PGA

Manufacturer

Freescale Semiconductor

Datasheet

1.MC68060RC50.pdf

(416 pages)

Specifications of MC68LC060RC66

Processor Type

M680x0 32-Bit

Speed

66MHz

Voltage

3.3V

Mounting Type

Surface Mount

Package / Case

206-PGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68LC060RC66

Manufacturer:

M/A-COM

Quantity:

101

- Current page: 346 of 416

- Download datasheet (2Mb)

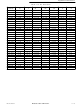

Electrical and Thermal Characteristics

12.6 OUTPUT AC TIMING SPECIFICATIONS (V

NOTES:

1. Output timing is measured at the pin, assuming a capacitive load of 50 pF. A maximum load of 130 pF may be used,

2. In a mixed supply system where the processor drives chips operating with 5-volt supply, the ÒPad Starts at 5.5 VÓ

3. BCLK is not a pin signal name. It is a virtual bus clock where the BCLK rising edge coincides with that of CLK when

4. When the processor drives these signals from a three-stated condition, use spec 11a or 40a. Use the ÒPad Starts at

5. ÒPad Starts at 5.5 V" does not apply since these signals are always driven.

12-4

Num

11a

40a

11

40

50

12

13

14

18

19

21

38

39

57

58

59

60

61

62

63

however. Characterization indicates that at 130 pF loads, output propagation delays are modified as follows: 50 MHz,

Pad at V

prop delay by 1.3; 66 MHz, pad at 5.5 V, multiply prop delay by 1.4. Exceeding the 130-pF limit on any pin may affect

long-term reliability and Motorola does not guarantee proper operation.

column should be used, as it is possible that a three-state pin is at 5.5 volts when the processor begins to drive it.

For a non three-state pin driven by the processor or a homogeneous 3.3-volt system, the ÒPad Starts at VccÓ column

must be used. This note does not apply to spec numbers 11, 11a, 40, and 40a. Refer to Note 5 for these specs.

CLKEN is asserted. The BCLK falling edge is insignificant. An output timing reference to BCLK means that the spe-

cific output transitions only on rising CLK edges when CLKEN is asserted. A timing reference to CLK means that the

output may transition off the rising CLK edge, regardless of CLKEN state.

V

are defined by spec 11 or 40. The ÒPad Starts at 5.5 VÓ column has no entry for specs 11 and 40, since the processor

only drives up to the V

4

4

5

CC

4

4

Ó column or ÒPad Starts at 5.5 VÓ column as appropriate. Once these signals are driven, subsequent transitions

BCLK to Address CIOUT, LOCK,

LOCKE, R/W, SIZx, TLN, TMx,

TTx, UPAx, BSx Valid (signal pre-

driven)

BCLK to Address CIOUT, LOCK,

LOCKE, R/W, SIZx, TLN, TMx,

TTx, UPAx, BSx Valid (signal from

three-state)

BCLK or CLK to Output Invalid

(Output Hold)

BCLK to TS Valid

BCLK to TIP Valid

BCLK to Data Out Valid

BCLK to Data Out Invalid (Output

Hold)

BCLK to Data-Out High Impedance

BCLK to Address, CIOUT, LOCK,

LOCKE, R/W, SIZx, TS, TLNx,

TMx, TTx, UPAx, BSx High Imped-

ance

CLK to BB, TIP High Impedance

BCLK to BR, BB Valid (Signal Pre-

driven)

BCLK to BB Valid (signal from

three-state)

CLK to IPEND, PSTx, RSTO Valid

BCLK to SAS Valid

BCLK to SAS Invalid (Output Hold)

BCLK to SAS High Impedance

BCLK to TS Invalid (Output Hold)

BCLK to BTT Valid

BCLK to BTT Invalid (Output Hold)

BCLK to BTT High Impedance

CC

, multiply prop delay by 1.4; 50 MHz, Pad at 5.5 V, multiply prop delay by 1.6; 66 MHz, Pad at V

Characteristic

CC

level. BR is never three-stated by the processor, and therefore, spec 40a does not apply.

Min Max Min Max Min Max Min Max Min Max Min Max

at 5.5 V

Ñ

Ñ

Ñ

Ñ

Ñ

Ñ

Ñ

Ñ

M68060 USERÕS MANUAL

2

2

2

2

2

2

2

2

2

2

2

2

Starts

Pad

15.4

14.4

15.4

13.5

15.4

15.4

15.4

12

12

12

12

12

Ñ

Ñ

Ñ

50 MHz

Ð

Ð

Ð

Ð

Ð

2

at V

Ñ

Ñ

Ñ

Ñ

Ñ

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

Starts

Pad

CC

12.6

13.5

12.3

13.5

13.5

12.6

13.5

13.5

13.5

13.5

12

12

12

12

12

Ð

Ð

Ð

Ð

Ð

2

at 5.5 V

Ñ

Ñ

Ñ

Ñ

Ñ

Ñ

Ñ

Ñ

2

2

2

2

2

2

2

2

2

2

2

2

Starts

Pad

11.8

10.9

11.8

10.4

11.8

11.8

11.8

10

10

10

10

10

Ñ

Ñ

Ñ

66 MHz

Ð

Ð

Ð

Ð

Ð

CC

2

at V

Ñ

Ñ

Ñ

Ñ

Ñ

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

= 3.3 V ± 5%)

Starts

Pad

CC

10.4 1.5 10.5 1.5

10.4 1.5 10.5 1.5

10.4 1.5

10.4 1.5 10.5 1.5

10.4

10.4 1.5 10.5 1.5

10.4 1.5 10.5 1.5

9.9

9.5

9.9

10

10

10

10

10

Ð

Ð

Ð

Ð

Ð

2

at 5.5 V

1.5

1.5

1.5

1.5

1.5

1.5

Ñ

Ñ

Ñ

Ñ

Ñ

Ñ

Ñ

Ñ

Starts

Pad

9.7

9.2

8.9

8.9

8.9

8.9

8.9

Ñ

Ñ

Ñ

75 MHz

Ð

Ð

Ð

Ð

Ð

2

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

at V

Ñ

Ñ

Ñ

Ñ

Ñ

Starts

CC

Pad

, multiply

CC

8.8

9.2

8.4

9.2

9.2

8.9

8.9

8.9

8.8

9.2

9.2

9.2

8.9

9.2

8.9

Ð

Ð

Ð

Ð

Ð

MOTOROLA

2

Unit

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

nS

Related parts for MC68LC060RC66

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: