CYP15G0401DXB-BGC Cypress Semiconductor Corp, CYP15G0401DXB-BGC Datasheet - Page 14

CYP15G0401DXB-BGC

Manufacturer Part Number

CYP15G0401DXB-BGC

Description

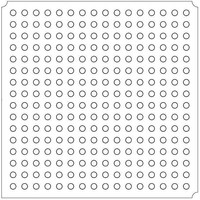

IC TXRX HOTLINK 256LBGA

Manufacturer

Cypress Semiconductor Corp

Series

HOTlink II™r

Type

Transceiverr

Datasheet

1.CYW15G0401DXB-BGXC.pdf

(53 pages)

Specifications of CYP15G0401DXB-BGC

Package / Case

256-LBGA Exposed Pad, 32-HLBGA

Number Of Drivers/receivers

4/4

Protocol

Multiprotocol

Voltage - Supply

3.135 V ~ 3.465 V

Mounting Type

Surface Mount

Product

PHY

Supply Voltage (min)

3.135 V

Supply Current

1.06 A

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Number Of Channels

4

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CYP15G0401DX-EVAL - IC TXRX HOTLINK 256-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

CY

Quantity:

767

Company:

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

CYPRESS

Quantity:

586

Company:

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Document #: 38-02002 Rev. *L

Pin Descriptions

CYP(V)(W)15G0401DXB Quad HOTLink II Transceiver

BISTLE

RXLE

BOE[7:0]

LFIA

LFIB

LFIC

LFID

Bonding Control

BONDST[1:0] Bidirectional Open Drain,

Pin Name

LVTTL Input,

asynchronous,

internal pull-up

LVTTL Input,

asynchronous,

internal pull-up

LVTTL Input,

asynchronous,

internal pull-up

LVTTL Output,

Asynchronous

internal pull-up

I/O Characteristics

(continued)

Transmit and Receive BIST Latch Enable. Active HIGH. When BISTLE = HIGH, the

signals on the BOE[7:0] inputs directly control the transmit and receive BIST enables.

When the BOE[x] input is LOW, the associated transmit or receive channel is

configured to generate or compare the BIST sequence respectively. When the BOE[x]

input is HIGH, the associated transmit or receive channel is configured for normal data

transmission or reception. The specific mapping of BOE[7:0] signals to transmit and

receive BIST enables is listed in Table 10. When BISTLE returns LOW, the last values

present on BOE[7:0] are captured in the internal BIST Enable Latch. When the latch

is closed, if the device is reset (TRSTZ is sampled LOW), the latch is reset to disable

BIST on all transmit and receive channels.

Receive Channel Power-control Latch Enable. Active HIGH. When RXLE = HIGH,

the signals on the BOE[7:0] inputs directly control the power enables for the receive

PLLs and analog circuitry. When the BOE[7:0] input is HIGH, the associated receive

channel A through D PLL and analog circuitry are active. When the BOE[7:0] input is

LOW, the associated receive channel A through D PLL and analog circuitry are

powered down. The specific mapping of BOE[7:0] signals to the associated receive

channel enables is listed in Table 10. When RXLE returns LOW, the last values

present on BOE[7:0] are captured in the internal RX PLL Enable Latch. When the

device is reset (TRSTZ = LOW), the latch is reset to disable all receive channels.

BIST, Serial Output, and Receive Channel Enables. These inputs are passed to

and through the Output Enable Latch when OELE is HIGH, and captured in this latch

when OELE returns LOW. These inputs are passed to and through the BIST Enable

Latch when BISTLE is HIGH, and captured in this latch when BISTLE returns LOW.

These inputs are passed to and through the Receive Channel Enable Latch when

RXLE is HIGH, and captured in this latch when RXLE returns LOW.

Link Fault Indication Output. Active LOW. LFIx is the logical OR of four internal

conditions:

Bonding Status. These signals are only used when multiple devices are bonded

together. They communicate the status of Elasticity Buffer management events from

master device of the bonding domain to the slave devices of the same bonding

domain. These outputs change at the same character rate as the receive output data

buses, but are connected only to all the slave CYP(V)(W)15G0401DXB devices.

When MASTER = LOW, these are output signals and present the Elasticity Buffer

status from the selected master receive channel of the device configured as the

master. Receive master channel selection is performed using the RXCLKB+ and

RXCLKD+ inputs. The BONDST[1:0] Outputs of the master device must be connected

to BONDST[1:0] Inputs of all the slave devices in the bonding domain. These status

outputs indicate one of four possible conditions, on a synchronous basis, to the slave

devices. These conditions are:

00—Reserved

01—Add one K28.5 immediately following the next framing character received

10—Delete next framing character received

11—Normal data.

These outputs are driven only when the device is configured as a master, all four

channels are bonded together, and the receive parallel interface is clocked by

REFCLK↑.

1. Received serial data frequency outside expected range

2. Analog amplitude below expected levels

3. Transition density lower than expected

4. Receive Channel disabled.

Signal Description

CYW15G0401DXB

CYP15G0401DXB

CYV15G0401DXB

Page 14 of 53