ISPPAC-POWR60401TE LATTICE [Lattice Semiconductor], ISPPAC-POWR60401TE Datasheet - Page 7

ISPPAC-POWR60401TE

Manufacturer Part Number

ISPPAC-POWR60401TE

Description

In-System Programmable Power Supply Sequencing Controller and Monitor

Manufacturer

LATTICE [Lattice Semiconductor]

Datasheet

1.ISPPAC-POWR60401TE.pdf

(29 pages)

Lattice Semiconductor

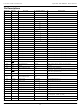

DC Input Levels: IN1-IN4

Transient Characteristics

PLD Timing

Digital Glitch

Filter

t

t

t

t

1. External clock 1MHz. Open drain outputs with 2k pull-up resistor to V

Note: All the above parameters apply to signal paths from the digital inputs [IN1-IN4].

CMOS, LVCMOS3.3, LVTTL, TTL

LVCMOS2.5

Note: V

V

CO

SU

H

t

RST

PD

DDINP.

Symbol

DDINP

is the input supply pin for IN1-IN4 digital logic input pins. The logic threshold trip point of IN1-IN4 is dependent on the voltage at

Standard

Minimum pulse width to transition through

glitch filter.

Clock to Out Delay. Rising edge of clock to

output transition.

Time that input needs to be present when

using a registered function with the clock.

Time that input needs to be held valid after

the clock edge when using a registered

function with the clock.

Propagation delay internal to the

embedded PLD

RESET pulse width

Parameter

Over Recommended Operating Conditions

Min.

-0.3

-0.3

V

IL

(V)

Applied to IN1-IN4

Stable input before

clock edge (Note 1)

Data valid before clock

(Note 1)

Hold data after clock

2-7

DD

Conditions

.

Max.

0.8

0.7

ispPAC-POWR604 Data Sheet

Min.

20

25

20

0

Min.

2.0

1.7

Typ.

V

IH

(V)

Max.

300

90

Max.

5.5

5.5

Units

µs

ns

µs

µs

ns

µs