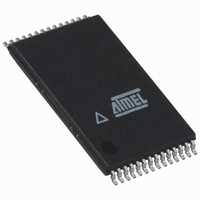

AT45DB642D-TU Atmel, AT45DB642D-TU Datasheet - Page 22

AT45DB642D-TU

Manufacturer Part Number

AT45DB642D-TU

Description

IC FLASH 64MBIT 66MHZ 28TSOP

Manufacturer

Atmel

Datasheet

1.AT45DB642D-CU.pdf

(58 pages)

Specifications of AT45DB642D-TU

Format - Memory

FLASH

Memory Type

DataFLASH

Memory Size

64M (8192 pages x 1056 bytes)

Speed

66MHz

Interface

Parallel/Serial

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

28-TSOP

Density

64Mb

Access Time (max)

6ns

Interface Type

Parallel/Serial-SPI

Boot Type

Not Required

Address Bus

1/8Bit

Operating Supply Voltage (typ)

3.3V

Operating Temp Range

-40C to 85C

Package Type

TSOP-I

Program/erase Volt (typ)

2.7 to 3.6V

Sync/async

Synchronous

Operating Temperature Classification

Industrial

Operating Supply Voltage (min)

2.7V

Operating Supply Voltage (max)

3.6V

Word Size

8b

Number Of Words

8M

Supply Current

15mA

Mounting

Surface Mount

Pin Count

28

Data Bus Width

8 bit

Architecture

Sectored

Supply Voltage (max)

3.6 V

Supply Voltage (min)

2.7 V

Maximum Operating Current

15 mA

Mounting Style

SMD/SMT

Organization

256 KB x 32

Memory Configuration

8192 Pages X 1056 Bytes

Clock Frequency

66MHz

Supply Voltage Range

2.7V To 3.6V

Memory Case Style

TSOP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT45DB642D-TU

Manufacturer:

MICRON

Quantity:

101

Company:

Part Number:

AT45DB642D-TU

Manufacturer:

ATMEL

Quantity:

9 396

Company:

Part Number:

AT45DB642D-TU

Manufacturer:

AT

Quantity:

5

Part Number:

AT45DB642D-TU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

11. Additional Commands

11.1

11.2

11.3

22

Main Memory Page to Buffer Transfer

Main Memory Page to Buffer Compare

Auto Page Rewrite

AT45DB642D

A page of data can be transferred from the main memory to either buffer 1 or buffer 2. To start

the operation for the standard DataFlash page size (1056 bytes), a 1-byte opcode, 53H for buf-

fer 1 and 55H for buffer 2, must be clocked into the device, followed by three address bytes

comprised of 13 page address bits (PA12 - PA0), which specify the page in main memory that is

to be transferred, and 11 don’t care bits. To perform a main memory page to buffer transfer for

the binary page size (1024 bytes), the opcode 53H for buffer 1 or 55H for buffer 2, must be

clocked into the device followed by three address bytes consisting of 13 page address bits (A22

- A10) which specify the page in the main memory that is to be transferred, and 10 don’t care

bits. The CS pin must be low while toggling the SCK/CLK pin to load the opcode and the

address bytes from the input pins (SI or I/O7 - I/O0). The transfer of the page of data from the

main memory to the buffer will begin when the CS pin transitions from a low to a high state. Dur-

ing the transfer of a page of data (t

monitored to determine whether the transfer has been completed.

A page of data in main memory can be compared to the data in buffer 1 or buffer 2. To initiate

the operation for standard DataFlash page size, a 1-byte opcode, 60H for buffer 1 and 61H for

buffer 2, must be clocked into the device, followed by three address bytes consisting of 13 page

address bits (PA12 - PA0) that specify the page in the main memory that is to be compared to

the buffer, and 11 don’t care bits. To start a main memory page to buffer compare for a binary

page size, the opcode 60H for buffer 1 or 61H for buffer 2, must be clocked into the device fol-

lowed by three address bytes consisting of 13 page address bits (A22 - A10) that specify the

page in the main memory that is to be compared to the buffer, and 10 don’t care bits. The CS pin

must be low while toggling the SCK/CLK pin to load the opcode and the address bytes from the

input pins (SI or I/O7 - I/O0). On the low-to-high transition of the CS pin, the data bytes in the

selected main memory page will be compared with the data bytes in buffer 1 or buffer 2. During

this time (t

completion of the compare operation, bit 6 of the status register is updated with the result of the

compare.

This mode is only needed if multiple bytes within a page or multiple pages of data are modified in

a random fashion within a sector. This mode is a combination of two operations: Main Memory

Page to Buffer Transfer and Buffer to Main Memory Page Program with Built-in Erase. A page of

data is first transferred from the main memory to buffer 1 or buffer 2, and then the same data

(from buffer 1 or buffer 2) is programmed back into its original page of main memory. To start the

rewrite operation for standard DataFlash page size (1056 bytes), a 1-byte opcode, 58H for buffer

1 or 59H for buffer 2, must be clocked into the device, followed by three address bytes com-

prised of 13 page address bits (PA12-PA0) that specify the page in main memory to be rewritten

and 11 don’t care bits. To initiate an auto page rewrite for a binary page size (1024 bytes), the

opcode 58H for buffer 1 or 59H for buffer 2, must be clocked into the device followed by three

address bytes consisting of 13 page address bits (A22 - A10) that specify the page in the main

memory that is to be written and 10 don’t care bits. When a low-to-high transition occurs on the

CS pin, the part will first transfer data from the page in main memory to a buffer and then pro-

gram the data from the buffer back into same page of main memory. The operation is internally

self-timed and should take place in a maximum time of t

and the RDY/BUSY pin will indicate that the part is busy.

COMP

), the status register and the RDY/BUSY pin will indicate that the part is busy. On

XFR

), the status register can be read or the RDY/BUSY can be

EP

. During this time, the status register

3542K–DFLASH–04/09