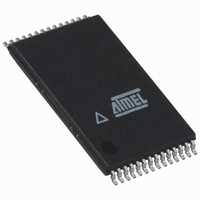

AT45DB642D-TU Atmel, AT45DB642D-TU Datasheet - Page 40

AT45DB642D-TU

Manufacturer Part Number

AT45DB642D-TU

Description

IC FLASH 64MBIT 66MHZ 28TSOP

Manufacturer

Atmel

Datasheet

1.AT45DB642D-CU.pdf

(58 pages)

Specifications of AT45DB642D-TU

Format - Memory

FLASH

Memory Type

DataFLASH

Memory Size

64M (8192 pages x 1056 bytes)

Speed

66MHz

Interface

Parallel/Serial

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

28-TSOP

Density

64Mb

Access Time (max)

6ns

Interface Type

Parallel/Serial-SPI

Boot Type

Not Required

Address Bus

1/8Bit

Operating Supply Voltage (typ)

3.3V

Operating Temp Range

-40C to 85C

Package Type

TSOP-I

Program/erase Volt (typ)

2.7 to 3.6V

Sync/async

Synchronous

Operating Temperature Classification

Industrial

Operating Supply Voltage (min)

2.7V

Operating Supply Voltage (max)

3.6V

Word Size

8b

Number Of Words

8M

Supply Current

15mA

Mounting

Surface Mount

Pin Count

28

Data Bus Width

8 bit

Architecture

Sectored

Supply Voltage (max)

3.6 V

Supply Voltage (min)

2.7 V

Maximum Operating Current

15 mA

Mounting Style

SMD/SMT

Organization

256 KB x 32

Memory Configuration

8192 Pages X 1056 Bytes

Clock Frequency

66MHz

Supply Voltage Range

2.7V To 3.6V

Memory Case Style

TSOP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT45DB642D-TU

Manufacturer:

MICRON

Quantity:

101

Company:

Part Number:

AT45DB642D-TU

Manufacturer:

ATMEL

Quantity:

9 396

Company:

Part Number:

AT45DB642D-TU

Manufacturer:

AT

Quantity:

5

Part Number:

AT45DB642D-TU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

21.8

Figure 21-2. Rapid8 Mode

21.9

Note:

40

MOSI = Master Out, Slave In

MISO = Master In, Slave Out

The Master would be the ASIC/MCU and the Slave would be the memory device.

The Master always clocks data out on the rising edge of SCK and always clocks data in on the falling edge of SCK.

The Slave always clocks data out on the falling edge of SCK and always clocks data in on the rising edge of SCK.

Slave

Utilizing the Rapid8

Reset Timing

The CS signal should be in the high state before the RESET signal is deasserted.

A.

B.

C.

D.

E.

F.

G. Master clocks in BYTE h (last output byte).

SO or I/O7 - I/O0

AT45DB642D

SI or I/O7 - I/O0

I/O

SCK

Master clocks out BYTE 1 on the rising edge of SCK.

Slave clocks in BYTE 1 on the next rising edge of SCK.

Master clocks out BYTE 2 on the same rising edge of SCK.

Slave clocks in BYTE 6 (last input byte).

Slave clocks out BYTE a (first output byte).

Master clocks in BYTE a.

CS

7-0

(OUTPUT)

SCK/CLK

(INPUT)

RESET

CS

A

The Rapid8 functions like RapidS but with 8 bits of data instead of 1 bit. A full clock cycle must

be used to transmit data back and forth across the 8 bit bus. The DataFlash is designed to

always clock its data out on the falling edge of the SCK signal and clock data in on the rising

edge of SCK.

For full clock cycle operation to be achieved, when the DataFlash is clocking data out on the fall-

ing edge of SCK, the host controller should wait until the next falling edge of SCK to latch the

data in. Similarly, the host controller should clock its data out on the rising edge of SCK in order

to give the DataFlash a full clock cycle to latch the incoming data in on the next rising edge of

SCK.

1

B

BYTE 1

C

2

™

BYTE 2

HIGH IMPEDANCE

Function

3

BYTE 3

4

BYTE 4

t

V

5

BYTE 5

6

BYTE 6

D

7

E

BYTE a

8

F

BYTE b

9

BYTE c

10

BYTE d

11

BYTE e

t RST

12

t REC

BYTE f

13

HIGH IMPEDANCE

BYTE g

14

G

BYTE h

15

t CSS

3542K–DFLASH–04/09