UPD70F3714GC-8BS-A Renesas Electronics America, UPD70F3714GC-8BS-A Datasheet - Page 528

UPD70F3714GC-8BS-A

Manufacturer Part Number

UPD70F3714GC-8BS-A

Description

MCU 32BIT V850ES/LX2 64-LQFP

Manufacturer

Renesas Electronics America

Series

V850ES/Ix2r

Datasheet

1.UPD70F3713GC-8BS-A.pdf

(674 pages)

Specifications of UPD70F3714GC-8BS-A

Core Processor

RISC

Core Size

32-Bit

Speed

20MHz

Connectivity

CSI, UART/USART

Peripherals

LVD, PWM, WDT

Number Of I /o

39

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

6K x 8

Voltage - Supply (vcc/vdd)

3.5 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPD70F3714GC-8BS-A

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 528 of 674

- Download datasheet (7Mb)

526

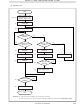

SIB0 pin capture

INTCB0R signal

(2) Operation timing

CB0SCE bit

CB0TSF bit

SCKB0 pin

SOB0 pin

SIB0 pin

(1) Write 00H to the CB0CTL1 register, and select communication type 1, communication clock (f

(2) Write 00H to the CB0CTL2 register, and set the transfer data length to 8 bits.

(3) Write A3H to the CB0CTL0 register, and select the reception mode, MSB first, and continuous transfer

(4) The CB0STR.CB0TSF bit is set to 1 by performing a dummy read of the CB0RX register, and

(5) When reception is started, output the serial clock to the SCKB0 pin, and capture the receive data of

(6) When reception is completed, the reception end interrupt request signal (INTCB0R) is generated, and

(7) When the CB0CTL0.CB0SCE bit = 1 upon communication completion, the next communication is

(8) To end continuous reception with the current reception, write the CB0SCE bit = 0.

(9) Read the CB0RX register.

(10) When reception is completed, the INTCB0R signal is generated, and reading of the CB0RX register is

(11) Read the CB0RX register.

(12) If an overrun error occurs, write the CB0STR.CB0OVE bit = 0, and clear the error flag.

(13) To release the reception enable status, write the CB0CTL0.CB0PWR bit = 0 and the

timing

f

mode at the same time as enabling the operation of the communication clock (f

reception is started.

the SIB0 pin in synchronization with the serial clock.

reading of the CB0RX register is enabled.

started following communication completion.

enabled. When the CB0SCE bit = 0 is set before communication completion, stop the serial clock

output to the SCKB0 pin, and clear the CB0TSF bit to 0, to end the receive operation.

CB0CTL0.CB0RXE bit = 0 after checking that the CB0TSF bit = 0.

XX

L

/2, and master mode.

(1)

(2)

(3)

(4)

(5)

Bit 7 Bit 6

CHAPTER 13 3-WIRE VARIABLE-LENGTH SERIAL I/O (CSIB)

Bit 5 Bit 4

Bit 3 Bit 2

User’s Manual U17716EJ2V0UD

Bit 1

(6) (7) (8) (9)

Bit 0

Bit 7 Bit 6

Bit 5 Bit 4

Bit 3 Bit 2

Bit 1

(10)

Bit 0

CCLK

).

(11) (13)

CCLK

) =

Related parts for UPD70F3714GC-8BS-A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: