UPD70F3714GC-8BS-A Renesas Electronics America, UPD70F3714GC-8BS-A Datasheet - Page 601

UPD70F3714GC-8BS-A

Manufacturer Part Number

UPD70F3714GC-8BS-A

Description

MCU 32BIT V850ES/LX2 64-LQFP

Manufacturer

Renesas Electronics America

Series

V850ES/Ix2r

Datasheet

1.UPD70F3713GC-8BS-A.pdf

(674 pages)

Specifications of UPD70F3714GC-8BS-A

Core Processor

RISC

Core Size

32-Bit

Speed

20MHz

Connectivity

CSI, UART/USART

Peripherals

LVD, PWM, WDT

Number Of I /o

39

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

6K x 8

Voltage - Supply (vcc/vdd)

3.5 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPD70F3714GC-8BS-A

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 601 of 674

- Download datasheet (7Mb)

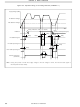

(4) Operation

Depending on the setting of the LVIM.LVIMD bit, an interrupt request signal (INTLVI) or an internal reset signal

is generated.

(a) To use for internal reset signal

If the supply voltage falls below the voltage detected by the low-voltage detector when LVI operation is

enabled, a system reset is executed (when the LVIM.LVIMD bit is set to 1), and the hardware is initialized

to the initial status.

The reset status lasts from when a supply voltage drop has been detected until the supply voltage rises

above the LVI detection voltage. Following reset release, the CPU starts program execution after securing

the oscillation stabilization time (initial value of OSTS register: 2

The main clock oscillator is stopped during the reset period, so secure the oscillation stabilization time.

The status of each hardware during the reset period and after reset release is the same as the reset

operation by the RESET pin (see 16.3.1 Reset operation via RESET pin). The following shows the

operation setting method and timing chart.

<To start operation>

<1> Mask the interrupt of LVI.

<2> Select the voltage to be detected by using the LVIS.LVIS0 bit.

<3> Set the LVIM. LVION bit to 1 (to enable operation).

<4> Insert a wait cycle of 0.1 ms (TYP) (target value) or more by software.

<5> By using the LVIM.LVIF bit, check if the supply voltage > detection voltage.

<6> Set the LVIM.LVIMD bit to 1 (to generate an internal reset signal).

Caution If the LVIMD bit is set to 1, the contents of the LVIM and LVIS registers cannot be changed

<To stop operation>

LVI operation cannot be stopped until a reset request is generated from other than LVI.

until a reset request other than LVI is generated.

CHAPTER 16 RESET FUNCTIONS

User’s Manual U17716EJ2V0UD

16

/f

X

) of the oscillator.

599

Related parts for UPD70F3714GC-8BS-A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: