XE1203FI063TRLF Semtech, XE1203FI063TRLF Datasheet - Page 18

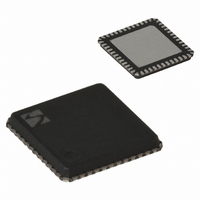

XE1203FI063TRLF

Manufacturer Part Number

XE1203FI063TRLF

Description

IC TXRX 433/868/915MHZ 48-VQFN

Manufacturer

Semtech

Specifications of XE1203FI063TRLF

Frequency

180MHz Center

Data Rate - Maximum

152.3kbps

Modulation Or Protocol

FSK

Applications

AMR, ISM, Home Automation, Process Control

Power - Output

0 ~ 15dBm

Sensitivity

-114dBm

Voltage - Supply

2.4 V ~ 3.6 V

Current - Receiving

14mA

Current - Transmitting

62mA

Data Interface

PCB, Surface Mount

Antenna Connector

PCB, Surface Mount

Operating Temperature

-40°C ~ 85°C

Package / Case

48-VQFN

Receiving Current

14mA

Transmitting Current

62mA

Data Rate

152.3Kbps

Modulation Type

FSK

No. Of Pins

48

Supply Voltage Range

2.4V To 3.6V

Operating Temperature Range

-40°C To +85°C

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Operating Temperature Classification

Industrial

Product Depth (mm)

7mm

Product Length (mm)

7mm

Operating Supply Voltage (typ)

2.5/3.3V

Operating Supply Voltage (max)

3.6V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Memory Size

-

Lead Free Status / Rohs Status

Compliant

Other names

XE1203FI063TR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XE1203FI063TRLF

Manufacturer:

SEMTECH

Quantity:

1 100

Company:

Part Number:

XE1203FI063TRLF

Manufacturer:

Semtech

Quantity:

2 300

Part Number:

XE1203FI063TRLF

Manufacturer:

SEMTECH/美国升特

Quantity:

20 000

5.1

5

A 3-wire bi-directional bus (SCK, SI, SO) is used to communicate with the XE1203F. SCK and SI are input signals

supplied externally, for example by the microcontroller. The XE1203F configures the SO signal as an output pin

during read operation, and it is tri-stated in other modes. The falling edge of the SCK signal is used to sample the

SI pin to write data into the internal shift register of the XE1203F. The rising edge of the SCK signal is used to

output data to SO pin by XE1203F, so the microcontroller should sample data at the falling edge of SCK.

The signal EN must be low during the whole write and read sequences. In write mode the content of the particular

configuration register (see 5.2) is updated on the next rising edge of the EN signal. Before this rising edge, the new

data is stored in temporary registers which do not affect the transceiver settings.

The timing diagram of a write sequence is illustrated in Figure 12

condition is detected, defined by the SI signal being set to “0” during one period of SCK. The next bit is a read/write

(R/W) bit which should be “0” to indicate a write operation. The next 5 bits contain the address of the

configuration/status registers A[4:0] to be accessed, MSB first (see 5.2). Then, the next 8 bits contain the data to

be written into the register. The sequence ends with 2 stop bits set to “1”. The data on SI should change on the

rising edges of SCK, and is sampled on the falling edge of SCK. After the 2 stop bits, the data transfer is

terminated. The SI line should be at “1” for at least one extra SCK clock cycle before a new write or read sequence

can start. This mode of operation allows data to be written into multiple registers keeping the EN line low.

The maximum frequency of SCK is 1 MHz, except as defined above when reading the RSSI or FEI outputs, where

the maximum frequency of SCK is limited to 100 kHz. The minimum clock pulse width is 0.5 us. Over the operating

supply and temperature range, set-up and hold time for SI on the falling edge of SCK are 200 ns.

The register at address 0 is one bit long. When writing this register, the sequence described above is valid except

that only one data bit is required instead of 8. However, if a single write procedure is used for all registers 8 data

bits must be sent when writing at address 0, but only the MSB will be stored at address 0. The remaining 7 data

bits must all be “1”.

Figure 13 illustrates a write sequence at address zero.

© Semtech 2008

SERIAL INTERFACE DEFINITION AND PRINCIPLES OF OPERATION

/en

si

SERIAL CONTROL INTERFACE

sck

so

A(4) A(3) A(2) A(1) A(0) D(7) D(6) D(5) D(4) D(3)

Figure 12: Write sequence into configuration register

High impedance

18

below. The sequence is initiated when a Start

D(2) D(1) D(0)

XE1203F

www.semtech.com