ISL6597CRZ Intersil, ISL6597CRZ Datasheet

ISL6597CRZ

Specifications of ISL6597CRZ

Related parts for ISL6597CRZ

ISL6597CRZ Summary of contents

Page 1

... PART RANGE PACKAGE (Note) MARKING (°C) ISL6597CRZ 65 97CRZ 4x4 QFN L16.4x4 Add “-T” suffix for tape and reel. NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations ...

Page 2

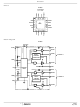

Pinout Block Diagram VCC VCTRL 3.5K PWM1 3.5K EN CONTROL LOGIC VCTRL 3.5K PWM2 3.5K GND 2 ISL6597 ISL6597 (16 LD QFN) TOP VIEW GND 17 LGATE1 2 11 PGND PVCC ...

Page 3

Typical Application - Multiphase Converter Using ISL6597 Gate Drivers COMP FB V VSEN CC ISEN1 PWM1 PGOOD EN PWM2 ISEN2 MAIN CONTROL ISL65xx VID ISEN3 FS/DIS PWM3 PWM4 GND ISEN4 3 ISL6597 BOOT1 +3.3V UGATE1 VCTRL PHASE1 +5V LGATE1 +3.3V ...

Page 4

Absolute Maximum Ratings Supply Voltage (PVCC, VCC -0. Input Voltage ( ...

Page 5

Electrical Specifications These specifications apply for T PARAMETER LGATE Fall Time UGATE Turn-Off Propagation Delay LGATE Turn-Off Propagation Delay UGATE Turn-On Propagation Delay LGATE Turn-On Propagation Delay Tri-state to UG/LG Rising Propagation Delay OUTPUT (Note 3) Upper Drive Source Resistance ...

Page 6

Timing Diagram t PWM PDHU t PDLU t RU UGATE LGATE 1V t PDLL Operation and Adaptive Shoot-Through Protection Designed for high speed switching, the ISL6597 MOSFET driver controls both high-side and low-side N-Channel FETs from one externally provided PWM ...

Page 7

... PWM line of ISL6597 (assuming an Intersil PWM controller is used). Bootstrap Considerations This driver features an internal bootstrap diode. Simply adding an external capacitor across the BOOT and PHASE pins completes the bootstrap circuit. The following equation helps select a proper bootstrap capacitor size: Q GATE ≥ ...

Page 8

PVCC BOOT HI1 LO1 G1 UGATE PHASE FIGURE 3. TYPICAL UPPER-GATE DRIVE TURN-ON PATH PVCC C GD LGATE R G HI2 R R LO2 R GI2 G2 GND FIGURE 4. TYPICAL LOWER-GATE DRIVE TURN-ON ...

Page 9

MOSFET to suppress the Miller coupling effect. The value of the resistor depends mainly on the input voltage’s rate of rise, the C /C ratio, as well as the gate-source GD GS threshold of the upper MOSFET. A higher ...

Page 10

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...