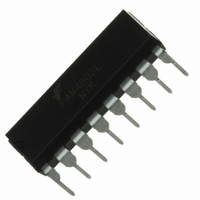

FAN4802LNY Fairchild Semiconductor, FAN4802LNY Datasheet - Page 20

FAN4802LNY

Manufacturer Part Number

FAN4802LNY

Description

IC PFC CTRLR AVERAGE CURR 16DIP

Manufacturer

Fairchild Semiconductor

Specifications of FAN4802LNY

Mode

Average Current

Frequency - Switching

64kHz

Current - Startup

30µA

Voltage - Supply

11 V ~ 22 V

Operating Temperature

-40°C ~ 105°C

Mounting Type

Through Hole

Package / Case

16-DIP (0.300", 7.62mm)

Operating Temperature (max)

105C

Operating Temperature (min)

-40C

Pin Count

16

Mounting

Through Hole

Screening Level

Industrial

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

© 2008 Fairchild Semiconductor Corporation

FAN4800A/C, FAN4801/02/02L • Rev. 1.0.3

Two-Level PFC Function

To improve the efficiency, the system can reduce PFC

switching loss at low line and light load by reducing the

PFC output voltage. The two-level PFC output of

FAN4801/02/02L can be programmable.

As Figure 47 shows, FAN4801/02/02L detect VEA pin

and VRMS pin to determine the system operates low

line and light load or not. At the second-level PFC, there

is a current of 20µA through R

the second-level PFC output voltage can be calculated

as.

For example, if the second-level PFC output voltage is

expected as 300V and normal voltage is 387V,

according to the equation, R

The programmable range of second level PFC output

voltage is 340V ~ 300V.

Oscillator (R

The oscillator frequency is determined by the values of

R

the oscillator output clock:

The dead time of the oscillator is derived from the

following equation:

at V

The dead time of the oscillator is determined using:

The dead time is so small (t

operating frequency can typically be approximated by:

Output

T

f

t

t

f

RT CT

RT CT

DEAD

RT CT

and C

REF

/

/

/

=7.5V and t

Figure 47. Two-Level PFC Scheme

T

7.78

R

, which determine the ramp and off-time of

C

t

t

2.8

RT CT

RT CT

F

T

1

R

1

V

mA

/

/

F

T

R

R

2

/C

T

F

1

RT/CT

2

T

C

t

ln

)

DEAD

T

(2.5

=CT x RT x 0.56.

VREF

VREF

360

V

F2

20

is 28kΩ R

C

F2

3.8

T

uA R

RT/CT

1

from FBPFC pin. So

>>t

F

F1

2

DEAD

)

is 4.3MΩ.

) that the

(4)

(5)

(6)

(7)

(3)

20

Pulse Width Modulator (PWM)

The operation of the PWM section is straightforward,

but there are several points that should be noted.

Foremost among these is the inherent synchronization

of PWM with the PFC section of the device, from which

it also derives its basic timing. The PWM is capable of

current-mode or voltage-mode operation. In current-

mode applications, the PWM ramp (RAMP) is usually

derived directly from a current sensing resistor or

current transformer in the primary of the output stage. It

is thereby representative of the current flowing in the

converter’s output stage. I

cycle current limiting, is typically connected to RAMP in

such applications. For voltage-mode operation and

certain

connected to a separate RC timing network to generate

a voltage ramp against which FBPWM is compared.

Under these conditions, the use of voltage feed-forward

from the PFC bus can assist in line regulation accuracy

and response. As in current-mode operation, the I

input is used for output stage over-current protection.

No voltage error amplifier is included in the PWM stage,

as this function is generally performed on the output

side of the PWM’s isolation boundary. To facilitate the

design of opto-coupler feedback circuitry, an offset has

been built into the PWM’s RAMP input that allows

FBPWM to command a 0% duty cycle for input voltages

below typical 1.5V.

PWM Cycle-By-Cycle Current Limiter

The ILIMIT pin is a direct input to the cycle-by-cycle

current limiter for the PWM section. Should the input

voltage at this pin ever exceed 1V, the output flip-flop is

reset by the clock pulse at the start of the next PWM

power cycle. When the I

bi-cycle current, it limits the PWM duty cycle mode and

the power dissipation is reduced during the dead-short

condition.

V

The V

PFC and inhibits the PWM if the voltage on FBPFC is

less than its nominal 2.4V. Once the voltage reaches

2.4V, which corresponds to the PFC output capacitor

being charged to its rated boost voltage, the soft-start

begins.

PWM Soft-Start (SS)

PWM startup is controlled by selection of the external

capacitor at soft-start. A current source of 10µA

supplies the charging current for the capacitor and

startup of the PWM begins at 1.5V.

IN

OK Comparator

IN

OK comparator monitors the DC output of the

specialized

applications,

LIMIT

LIMIT

triggers the cycle-by-cycle

, which provides cycle-by-

RAMP

www.fairchildsemi.com

can

LIMIT

be