ISL6549CAZA-T Intersil, ISL6549CAZA-T Datasheet - Page 10

ISL6549CAZA-T

Manufacturer Part Number

ISL6549CAZA-T

Description

IC CTRLR PWM SYNC BUCK 16-QSOP

Manufacturer

Intersil

Datasheet

1.ISL6549CAZR5213.pdf

(18 pages)

Specifications of ISL6549CAZA-T

Pwm Type

Voltage Mode

Number Of Outputs

2

Frequency - Max

1MHz

Duty Cycle

100%

Voltage - Supply

4.75 V ~ 13.2 V

Buck

Yes

Boost

No

Flyback

No

Inverting

No

Doubler

No

Divider

No

Cuk

No

Isolated

No

Operating Temperature

0°C ~ 70°C

Package / Case

16-QSOP

Frequency-max

1MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

ISL6549CAZA-TTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ISL6549CAZA-T

Manufacturer:

INTERSIL

Quantity:

20 000

For most situations, no external compensation is required for

the linear output. See “Linear Controller Feedback

Compensation” on page 12.

For both outputs, the selection of 1% resistors may not be

able to get the exact ratio desired for any given output voltage.

If the output must be defined better, then one option is to

place a much bigger resistor in parallel with R4 or R6, to lower

its value. For example, a 100kΩ in parallel with a 1.00kΩ

yields 990Ω, 1% below 1.00kΩ, which gives finer resolution

than the next lower size (976Ω 1%). The big resistor may not

have to be 1% tolerance either.

If the linear output is not required, connect the LDO_DR pin

directly to LDO_FB pin with no other components. This will

terminate the signals and keep the linear from tripping its

undervoltage, which would force both outputs into retry.

Converter Shutdown

Pulling and holding the FS_DIS pin near GND will shut down

both regulators; almost any NFET or other pull-down device

(<1kΩ impedance) should work. Upon release of the FS_DIS

pin, the regulators enter into a soft-start cycle which brings

both outputs back into regulation. The FS_DIS pin requires a

quiet GND to minimize jitter. To accomplish this, the FS

resistor and any pull-down device should be placed as close

as possible to the pin, and the GND should be kept away from

the noisy FET GND.

Boot Capacitor, Boot Refresh

A capacitor from the PHASE pin to the BOOT pin is required

for the bootstrap circuit for the Upper Gate. The V

(and thus the PHASE node) is allowed to go as high as a

nominal 12V (±10%) supply. A diode is included on the IC

(anode to PVCC5 pin, cathode to BOOT pin), such that the

PVCC5 (nominally around 5.25V) will be the bootstrap supply.

In the event that the UGATE is on for an extended period of

time, the charge on the boot capacitor can start to sag, raising

the R

detects a long UGATE on-time (32 oscillator clock periods),

V

C

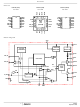

FIGURE 8. OUTPUT VOLTAGE SELECTION OF THE LINEAR

OUT2

OUT2

V

IN2

DS(ON)

+

C

IN2

of the upper FET. The ISL6549 has a circuit that

V

(V

OUT2

+

OUT2

Q3

)

=

0.8

×

R5

⎛

⎝

1

10

+

R5

------- -

R6

⎞

⎠

R6

LDO_DR

LDO_FB

ISL6549

IN1

voltage

ISL6549

and forces the LGATE to go high for one oscillator cycle,

which allows the bootstrap capacitor time to recharge.

PWM Controller Feedback Compensation

This section highlights the design consideration for a

voltage-mode controller requiring external compensation. To

address a broad range of applications, a type-3 feedback

network is recommended (see Figure 9).

Figure 10 highlights the voltage-mode control loop for a

synchronous-rectified buck converter, applicable to the

ISL6549 circuit. The output voltage (V

reference voltage, VREF. The error amplifier output (COMP pin

voltage) is compared with the oscillator (OSC) modified

saw-tooth wave to provide a pulse-width modulated wave with

an amplitude of V

smoothed by the output filter (L and C). The output filter

capacitor bank’s equivalent series resistance is represented by

the series resistor E.

The modulator transfer function is the small-signal transfer

function of V

gain, given by d

filter, with a double pole break frequency at F

F

channel inductance and its DCR, while C and E represents

the total output capacitance and its equivalent series

resistance.

The compensation network consists of the error amplifier

(internal to the ISL6549) and the external R1-R3, C1-C3

components. The goal of the compensation network is to

provide a closed loop transfer function with high 0dB crossing

frequency (F

margin (better than 45 degrees). Phase margin is the difference

between the closed loop phase at F

equations that follow relate the compensation network’s poles,

zeros and gain to the components (R1, R2, R3, C1, C2, and

C3) in Figure 10.

F

CE

LC

FIGURE 9. COMPENSATION CONFIGURATION FOR ISL6549

. For the purpose of this analysis, L and D represent the

=

---------------------------

2π

⋅

R1

1

L C

OUT

0

; typically 0.1 to 0.3 of F

⋅

CIRCUIT

MAX

R2

/V

IN

COMP

at the PHASE node. The PWM wave is

V

C2

IN

R3

C3

C1

/V

. This function is dominated by a DC

OSC

F

CE

COMP

, and shaped by the output

=

----------------------- -

2π C E

FB

0dB

⋅

SW

OUT

1

V

and 180°. The

⋅

DIFF

) and adequate phase

) is regulated to the

ISL6549

(V

LC

OUT

September 22, 2006

and a zero at

)

FN9168.2

(EQ. 3)