CY3220LINBUS-RD Cypress Semiconductor Corp, CY3220LINBUS-RD Datasheet - Page 5

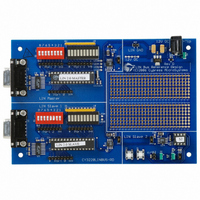

CY3220LINBUS-RD

Manufacturer Part Number

CY3220LINBUS-RD

Description

KIT REF DESIGN LIN BUS

Manufacturer

Cypress Semiconductor Corp

Series

PSoC®r

Datasheet

1.CY3220LINBUS-RD.pdf

(64 pages)

Specifications of CY3220LINBUS-RD

Main Purpose

Interface, LIN

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

CY8C27143, CY8C27443

Processor To Be Evaluated

CY8C27143-24PXI and CY8C27443-24PXI

Interface Type

RS-232

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Other names

428-1926

LIN Bus 2.0 Reference Design

5.1 Demonstration Projects Introduction ...............................................................................................43

6.1 Board Schematics ..............................................................................................................................57

7.1 Board Bill of Materials .......................................................................................................................61

4.7

4.8

5.2

5.3

5.4

5.5

4.6.6

4.6.7

4.6.8

4.6.9

4.6.10

LIN 2.0 Slave Design API ........................................................................................................39

Time Study ...............................................................................................................................40

4.8.1

4.8.2

4.8.3

LIN Description File (LDF)........................................................................................................43

5.2.1

5.2.2

Example Project for Master (CEM) ..........................................................................................47

5.3.1

5.3.2

Example Project for Slave 1 (CPM) .........................................................................................52

5.4.1

5.4.2

Example Project for Slave 2 (DIA) ...........................................................................................54

5.5.1

5.5.2

6.1.1

6.1.2

6.1.3

6.1.4

4.6.5.1

Frame Definition.....................................................................................................37

Response_Error Bit Definition................................................................................37

Node Information ...................................................................................................37

Adding the Main Application ..................................................................................37

Special Features ....................................................................................................38

4.6.10.1

4.6.10.2

4.6.10.3

ISR and Function Timing .......................................................................................40

Calculation of CPU Overhead Over a Frame.........................................................41

Maximum Interrupt Latency ...................................................................................41

Description .............................................................................................................43

Example LDF .........................................................................................................44

Description .............................................................................................................47

Example Master Program ......................................................................................47

Description .............................................................................................................52

Example Slave 1 Program .....................................................................................52

Description .............................................................................................................54

Example Slave 2 Program .....................................................................................54

Power Supply.........................................................................................................57

Master ....................................................................................................................58

Slave 1 ...................................................................................................................59

Slave 2 ...................................................................................................................60

RAM Allocation ....................................................................................36

Power Management.............................................................................38

Node Configuration..............................................................................38

Implementing Event-Triggered Frames ...............................................38

Contents

3