XC4VFX40-10FFG1152C Xilinx Inc, XC4VFX40-10FFG1152C Datasheet - Page 261

XC4VFX40-10FFG1152C

Manufacturer Part Number

XC4VFX40-10FFG1152C

Description

IC FPGA VIRTEX-4 FX 40K 1152FBGA

Manufacturer

Xilinx Inc

Series

Virtex™-4r

Specifications of XC4VFX40-10FFG1152C

Number Of Logic Elements/cells

41904

Number Of Labs/clbs

4656

Total Ram Bits

2654208

Number Of I /o

448

Voltage - Supply

1.14 V ~ 1.26 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

1152-BBGA, FCBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC4VFX40-10FFG1152C

Manufacturer:

TI

Quantity:

2 210

Company:

Part Number:

XC4VFX40-10FFG1152C

Manufacturer:

Xilinx Inc

Quantity:

10 000

- Current page: 261 of 406

- Download datasheet (6Mb)

Virtex-4 FPGA User Guide

UG070 (v2.6) December 1, 2008

GTL (Gunning Transceiver Logic)

R

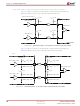

GTL_DCI Usage

The Gunning Transceiver Logic (GTL) standard is a high-speed bus standard (JESD8.3)

invented by Xerox. Xilinx has implemented the terminated variation for this standard. This

standard requires a differential amplifier input buffer and an open-drain output buffer.

The negative terminal of the differential input buffer is referenced to the V

A sample circuit illustrating a valid termination technique for GTL with external parallel

termination and unconnected V

GTL does not require a V

1.2V. GTL_DCI provides single termination to V

A sample circuit illustrating a valid termination technique for GTL_DCI with internal

parallel driver and receiver termination is shown in

Table 6-10

Table 6-10: GTL DC Voltage Specifications

V

V

V

V

V

V

V

V

I

I

OH

OL

CCO

CCO

REF

TT

IH

IL

OH

OL

Figure 6-36: GTL_DCI with Internal Parallel Driver and Receiver Termination

Figure 6-35: GTL with External Parallel Termination and Unconnected V

= V

at V

at V

= V

= Unconnected

= N × V

REF

REF

OL

OH

lists the GTL DC voltage specifications.

V

Parameter

(mA) at 0.4V

– 0.05

+ 0.05

(mA)

CCO

TT

(1)

= 1.2V

IOB

R VRP = Z 0 = 50Ω

Specific Guidelines for Virtex-4 FPGA I/O Supported Standards

R

P

= Z 0 = 50Ω

CCO

www.xilinx.com

voltage. However, for GTL_DCI, V

IOB

V

CCO

TT

= 1.2V

is shown in

Min

0.74

1.14

0.79

Z 0 = 50

32

Z 0 = 50

–

–

–

–

–

V

TT

= 1.2V

CCO

Figure

R

P

for inputs or outputs.

Figure

= Z 0 = 50Ω

IOB

6-35.

N/A

Typ

0.85

0.75

V

0.8

1.2

0.2

–

–

–

REF

6-36.

V

CCO

= 0.8V

V

CCO

IOB

REF

= 1.2V

R VRP = Z 0 = 50Ω

must be connected to

= 0.8V

UG070_6_34_031308

Max

+

0.86

1.26

0.81

–

0.4

–

–

–

–

-

REF

UG070_6_33_031308

pin.

+

–

CCO

261

Related parts for XC4VFX40-10FFG1152C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC FPGA VIRTEX-4 FX 40K 672-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4 FX 40K 672-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4 FX 40K 672-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4 FX 40K 1152FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4 FX 40K 1152FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4 FX 40K 672-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4 FX 40K 1152FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4 FX 40K 1152FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4FX 1152FFBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4FX 672FFBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-4FX 1152FFBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

FPGA Virtex®-4 Family 41904 Cells 90nm (CMOS) Technology 1.2V 672-Pin FCBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC CPLD .8K 36MCELL 44-VQFP

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC CPLD 72MCRCELL 10NS 44VQFP

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC CPLD 1.6K 72MCELL 64-VQFP

Manufacturer:

Xilinx Inc

Datasheet: