cy28443oxc-3t SpectraLinear Inc, cy28443oxc-3t Datasheet

cy28443oxc-3t

Related parts for cy28443oxc-3t

cy28443oxc-3t Summary of contents

Page 1

Features ® • Compliant to Intel CK410M • Selectable CPU frequencies • Differential CPU clock pairs • 100 MHz differential SRC clocks • 96 MHz differential dot clock • 27 MHz Spread and Non-spread video clock • 48 MHz USB ...

Page 2

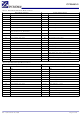

Pin Descriptions Pin No. Name 1, 7, 11, 21, VDD 28, 34, 42 13, 29, VSS 45, 51 3,4 PCI[3:4] 5 PCI5/FCTSEL1 8 ITP_SEL/PCIF0 9 PCIF1 10 VTT_PWRGD#/PD 12 FSA/48M 14, 15 DOT96T/27M_non spread DOT96C/27M_Spread 16 FSB ...

Page 3

Pin Descriptions (continued) Pin No. Name 52 REF1/FCTSEL0 53 FSC 54 CPU_STP# 55 PCI_STP# 56 PCI2/SEL_CLKREQ# I/O, PD Table 1. Frequency Select Table FSA, FSB and FSC FSC FSB FSA CPU 100 MHz 133 ...

Page 4

Table 3. Block Read and Block Write Protocol Block Write Protocol Bit Description 1 Start 8:2 Slave address – 7 bits 9 Write 10 Acknowledge from slave 18:11 Command Code – 8 bits 19 Acknowledge from slave 27:20 Byte Count ...

Page 5

Control Registers Byte 0: Control Register 0 Bit @Pup 7 1 RESERVED 6 1 RESERVED RESERVED 0 1 /100M[T/C]_SST Byte 1: Control Register 1 Bit @Pup ...

Page 6

Byte 3: Control Register 3 Bit @Pup 7 0 RESERVED 6 0 RESERVED RESERVED 0 0 Byte 4: Control Register 4 Bit @Pup 7 0 100M[T/C]_SST 6 0 DOT96[T/C] 5 ...

Page 7

Byte 5: Control Register 5 (continued) Bit @Pup Byte 6: Control Register 6 Bit @Pup 7 0 TEST_SEL 6 0 TEST_MODE PCI, PCIF and SRC clock outputs except those set ...

Page 8

Byte 8: Control Register 8 (continued) Bit @Pup 1 1 RESERVED 0 1 PCIF0 Byte 9: Control Register 9 Bit @Pup RESERVED 2 1 27M Spread ...

Page 9

Byte 11: Control Register 11 Bit @Pup 7 0 RESERVED 6 HW RESERVED 5 HW RESERVED 4 HW RESERVED 3 0 27MHz 2 0 RESERVED 1 0 RESERVED 0 HW RESERVED Byte 12: Control Register 12 Bit @Pup 7 0 ...

Page 10

Byte 14: Control Register 14 (continued) Bit @Pup 3 0 CLKREQ CLKREQ CLKREQ CLKREQ#A Byte 15: Control Register 15 Bit @Pup 7 1 CLKREQ RESERVED 5 0 RESERVED 4 0 CLKREQ#B 3 ...

Page 11

Table 5. Crystal Recommendations Frequency (Fund) Cut Loading Load Cap 14.31818 MHz AT Parallel The CY28443-3 requires a Parallel Resonance Crystal. Substituting a series resonance crystal will cause the CY28443-3 to operate at the wrong frequency and violate the ppm ...

Page 12

All stopped SRC outputs must be driven HIGH within CLKREQ#[1:0] deassertion to a voltage greater than 200 mV. CLK_REQ[A:B]# Deassertion (CLKREQ# -> HIGH) The impact of deasserting the CLKREQ#[A:B] pins is all SRC outputs that are ...

Page 13

PD CPUT, 133MHz CPUC, 133MHz SRCT 100MHz SRCC 100MHz USB, 48MHz DOT96T DOT96C PCI, 33 MHz REF CPU_STP# Assertion The CPU_STP# signal is an active LOW input used for synchronous stopping and starting the CPU output clocks while the rest ...

Page 14

CPU_STOP# PD CPUT(Free Running CPUC(Free Running CPUT(Stoppable) CPUC(Stoppable) DOT96T DOT96C Figure 8. CPU_STP#= Driven, CPU_PD = Driven, DOT_PD = Driven CPU_STOP# PD CPUT(Free Running) CPUC(Free Running) CPUT(Stoppable) CPUC(Stoppable) DOT96T DOT96C Figure 9. CPU_STP# = Tri-state, CPU_PD = Tri-state, DOT_PD = ...

Page 15

PCI_STP# PCI_F PCI SRC 100MHz FS_A, FS_B,FS_C VTT_PWRGD# PWRGD_VRM VDD Clock Gen Clock State State 0 Off Clock Outputs Off Clock VCO VDD_A = 2.0V S0 Power Off Figure 13. Clock Generator Power-up/Run State Diagram Rev 1.0, November 20, 2006 ...

Page 16

Absolute Maximum Conditions Parameter Description V Core Supply Voltage DD V Analog Supply Voltage DD_A V Input Voltage IN T Temperature, Storage S T Temperature, Operating Ambient A T Temperature, Junction J Ø Dissipation, Junction to Case JC Ø Dissipation, ...

Page 17

AC Electrical Specifications Parameter Description Crystal T XIN Duty Cycle DC T XIN Period PERIOD XIN Rise and Fall Times XIN Cycle to Cycle Jitter CCJ L Long-term Accuracy ACC CPU at 0.7V T ...

Page 18

AC Electrical Specifications Parameter Description V Crossing Point Voltage at 0.7V Swing OX V Maximum Overshoot Voltage OVS V Minimum Undershoot Voltage UDS V Ring Back Voltage RB SRC T SRCT and SRCC Duty Cycle DC T 100-MHz SRCT and ...

Page 19

AC Electrical Specifications Parameter Description SSCT and SSCC Rise and Fall Time Rise/Fall Matching RFM T Rise TimeVariation R T Fall Time Variation F V Voltage High HIGH V Voltage Low LOW V Crossing ...

Page 20

AC Electrical Specifications Parameter Description 48_M at 3.3V T Duty Cycle DC T Period PERIOD T Absolute Period PERIODAbs T 48_M High time HIGH T 48_M Low time LOW Rising and Falling Edge Rate ...

Page 21

Test and Measurement Set-up For PCI Single-ended Signals and Reference The following diagram shows test load configurations for the single-ended PCI, USB, and REF output signals. PCI/ USB REF Figure 14.Single-ended Load Configuration Low Drive Option Figure 15. Single-ended Load ...

Page 22

... Figure 17. Single-ended Output Signals (for AC Parameters Measurement) Ordering Information Part Number Lead-free CY28443OXC-3 56-pin SSOP CY28443OXC-3T 56-pin SSOP – Tape and Reel CY28443ZXC-3 56-pin TSSOP CY28443ZXC-3T 56-pin TSSOP – Tape and Reel Rev 1.0, November 20, 2006 ...

Page 23

Package Diagrams 56-Lead Thin Shrunk Small Outline Package, Type mm) Z56 0.249[0.009 13.894[0.547] 14.097[0.555] 0.851[0.033] 0.500[0.020] 0.950[0.037] BSC 28 29 0.088 0.092 0.025 BSC While SLI has reviewed all information herein for accuracy ...