cy2sstu32864 SpectraLinear Inc, cy2sstu32864 Datasheet

cy2sstu32864

Available stocks

Related parts for cy2sstu32864

cy2sstu32864 Summary of contents

Page 1

... All clock and data inputs are compatible with the JEDEC standard for SSTL_18. The control inputs are LVCMOS. All outputs are 1.8V CMOS drivers that have been optimized to drive the DDR-II DIMM load. The CY2SSTU32864 operates from a differential clock (CK and CK#). Data are registered at the crossing of CK going high, and CK# going low. ...

Page 2

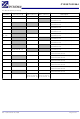

... B5 E5, F5, K5, L5, M5 E5, F5, K5, L5, M5 Data Outputs that are suspended by the DCS# N5 CY2SSTU32864 Description Ground Power Supply Voltage Input Reference Voltage Reserved Reserved Positive Master Clock Negative Master Clock Configuration Control Input Configuration Control Input Asynchronous Reset – resets registers and ...

Page 3

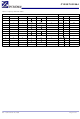

... T6 A2, B2, C2, D2, E2, F2, G1, K2, L2, E2, F2, G1, K2, L2, M2, N2, P2, R2, T2 M2, N2, P2, R2, T2 CY2SSTU32864 Description Data Outputs that are suspended by the DCS# and CSR# control Data Outputs that are suspended by the DCS# and CSR# control Data Outputs that are suspended by the DCS# ...

Page 4

... Floating X or Floating X or Floating Rev 1.0, November 25, 2006 Inputs CK CK# Dn, DODT, DCKE Floating X or Floating CY2SSTU32864 Outputs Qn QCS# QODT, QCKE ...

Page 5

... mA 1. –100 1. – RESET RESET IH(AC 1.9V DD CY2SSTU32864 Min. –0.5 V –0.5 V –65 –0.5 –50 DD –50 DD –50 –100 Min. 0 1.7 0.675 600 0.49*V 0.51 – REF REF 0 –5 – V REF – ...

Page 6

... DCS#, CSRT#, ODT, CKE and data after crossing CK,CK#, CK going high From CK, CK From CK, CK – simultaneous switching RESET# Start to Q Low dv/dt_r (20 to 80%) dv/dt_f (20 to 80%) max, after RESET# is taken high. ACT CY2SSTU32864 Min CK, 28 (typical) IL(AC CK, 18 (typical) IL(AC ...

Page 7

... Figure 1. Test Load for Timing Measurements #1 DUT OUT DUT OUT C = 10pF L RESET VDD/2 Input D t inact Figure 4. Active and Inactive Times t w Input V ICR Figure 5. Pulse Duration CY2SSTU32864 VDD R = 1000 L Test Point R = 1000 C = 30pF L L VDD Test Point C = 10pF L Test Point ...

Page 8

... V Input REF Figure 6. Set-up and Hold Times CK V ICR CK t PLH V TT Figure 7. Propagation Delay RESET# VDD/2 Output Figure 8. Propagation Delay after RESET# CY2SSTU32864 VID VIH V REF VIL V VID ICR t PHL VOH V TT VOL VIH VIL t RPHL VOH V TT ...

Page 9

... Rev 1.0, November 25, 2006 Package Type 96-pin FBGA 96-pin FBGA– Tape and Reel 96 FBGA (5.5 x 13.5 x 1.2 mm) BA96A 6 A CY2SSTU32864 Product Flow Commercial, 0° to 85°C Commercial, 0° to 85°C Ø0. Ø0. Ø0.50±0.05(96X) BOTTOM VIEW ...