saa569x NXP Semiconductors, saa569x Datasheet - Page 25

saa569x

Manufacturer Part Number

saa569x

Description

Enhanced Tv Microcontrollers With On-screen Display Osd

Manufacturer

NXP Semiconductors

Datasheet

1.SAA569X.pdf

(116 pages)

- Current page: 25 of 116

- Download datasheet (533Kb)

Philips Semiconductors

2002 May 06

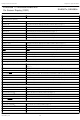

Timer/counter Control Register (TCON)

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

Timer/counter2 Control Register (T2CON)

TF2

EXF2

RCLK0

TCLK0

EXEN2

TR2

C/T2

CP/RL2

14-bit PWM MSB Register (TDACH)

TPWE

TD13 to TD8

14-bit PWM LSB Register (TDACL)

TD7 to TD0

Timer 0 High byte (TH0)

TH07 to TH00

Enhanced TV microcontrollers with

On-Screen Display (OSD)

BITS

Timer 1 overflow flag: Set by hardware on Timer/counter overflow. Cleared by

hardware when processor vectors to interrupt routine.

Timer 1 run control bit: Set/cleared by software to turn Timer/counter on/off.

Timer 0 overflow flag: Set by hardware on Timer/counter overflow. Cleared by

hardware when processor vectors to interrupt routine.

Timer 0 run control bit: Set/cleared by software to turn Timer/counter on/off.

Interrupt 1 edge flag. Both edges generate flag. Set by hardware when external

interrupt edge detected. Cleared by hardware when interrupt processed.

Interrupt 1 type control bit: Set/cleared by software to specify edge/low level

triggered external interrupts.

Interrupt 0 Edge l flag: Set by hardware when external interrupt edge detected.

Cleared by hardware when interrupt processed.

Interrupt 0 type flag: Set/cleared by software to specify falling edge/low level

triggered external interrupts.

Timer 2 overflow flag: Cleared by software. TF2 will not be set when either

baud rate generation mode or clock out mode.

Timer 2 External Flag: Set on a negative transition on T2EX and EXEN2 = 1. In

Auto-reload mode it is toggled on an under or overflow. Cleared by software.

Receive clock 0 flag: When set, causes the UART to use Timer 2 overflow

pulses. RCLK0 = 0 causes Timer 1 overflow pulses to be used.

Transmit clock 0 flag: When set, causes the UART to use Timer 2 overflow

pulses. TCLK0 = 0 causes Timer 1 overflow pulses to be used.

Timer 2 external enable flag: when set, allows a capture or reload to occur,

together with an interrupt, as a result of a negative transition on input T2EX if in

capture mode or Auto-reload mode with DCEN reset. If in Auto-reload mode and

DCEN is set, this bit has no influence. In the other modes, EXF2 is set and an

interrupt is generated on a HIGH-to-LOW transition on T2EX pin. In all modes,

EXEN2 = 0 causes Timer 2 to ignore events at T2EX.

START/STOP control bit: a logic 1 starts Timer 2

Counter Timer selection bit: a logic 1 selects the counter for Timer 2

Capture/Reload flag: selection of mode capture or reload

activate this 14-bit PWM (logic 1)

6 MSBs of 14-bit number to be output by the 14-bit PWM

8 LSBs of 14-bit number to be output by the 14-bit PWM

8 MSBs of Timer 0 16-bit counter

25

FUNCTION

SAA567x; SAA569x

Objective specification

Related parts for saa569x

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

NXP Semiconductors designed the LPC2420/2460 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2458 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2468 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2470 microcontroller, powered by theARM7TDMI-S core, to be a highly integrated microcontroller for a wide range ofapplications that require advanced communications and high quality graphic displays

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2478 microcontroller, powered by theARM7TDMI-S core, to be a highly integrated microcontroller for a wide range ofapplications that require advanced communications and high quality graphic displays

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The Philips Semiconductors XA (eXtended Architecture) family of 16-bit single-chip microcontrollers is powerful enough to easily handle the requirements of high performance embedded applications, yet inexpensive enough to compete in the market for hi

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The Philips Semiconductors XA (eXtended Architecture) family of 16-bit single-chip microcontrollers is powerful enough to easily handle the requirements of high performance embedded applications, yet inexpensive enough to compete in the market for hi

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The XA-S3 device is a member of Philips Semiconductors? XA(eXtended Architecture) family of high performance 16-bitsingle-chip microcontrollers

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP BlueStreak LH75401/LH75411 family consists of two low-cost 16/32-bit System-on-Chip (SoC) devices

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP LPC3130/3131 combine an 180 MHz ARM926EJ-S CPU core, high-speed USB2

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP LPC3141 combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3143 combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3152 combines an 180 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3154 combines an 180 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

Standard level N-channel enhancement mode Field-Effect Transistor (FET) in a plastic package using NXP High-Performance Automotive (HPA) TrenchMOS technology

Manufacturer:

NXP Semiconductors

Datasheet: