saa569x NXP Semiconductors, saa569x Datasheet - Page 48

saa569x

Manufacturer Part Number

saa569x

Description

Enhanced Tv Microcontrollers With On-screen Display Osd

Manufacturer

NXP Semiconductors

Datasheet

1.SAA569X.pdf

(116 pages)

Philips Semiconductors

18 UART PERIPHERAL

The 80C51 microcontroller incorporates a full duplex

UART with a single byte receive buffer, meaning that it can

commence reception of a second byte before the first is

read from the receive buffer. This register is implemented

twice. Writing to S0BUF writes to the transmit buffer.

Reading from S0BUF reads from the receive buffer. Only

hardware can read from the transmit buffer and write to the

receive buffer.

For further details refer to the “SAA56xx UART Operation

Application Note SPG/AN01010” .

The UARTs TX and RX pins connect to P0.1 and P0.0,

respectively.

Two registers (S0CON, S0BUF) and one bit (SMOD in

PCON register) control the UART.

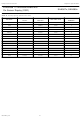

Table 20 UART Special Function Registers

18.1

The serial port can operate in four modes:

2002 May 06

Mode 0: Serial data enters and exits through RX. TX

outputs the shift clock. Eight bits are transmitted and

received (LSB first). The baud rate is fixed at

Mode 1: Ten bits are transmitted (through TX) or

received (through RX): a start bit (logic 0), eight data bits

(LSB first) and a stop bit (logic 1). On receive, the stop

bit goes into RB8 in SFR S0CON. The baud rate can be

varied at either Timer 1 or 2 overflow rate.

Mode 2: Eleven bits are transmitted (through TX) or

received (through RX): start bit (logic 0), eight data bits

(LSB first), a 9

On transmit, the 9

assigned the value of logic 0 or logic 1. For example, the

parity bit could be moved into TB8. On receive, the 9

data bit goes into RB8 in S0CON, while the stop bit is

ignored. The baud rate can be programmed to either

1

Mode 3: Eleven bits are transmitted (through TX) or

received (through RX): a start bit (logic 0), eight data bits

(LSB first), a 9

Mode 3 is the same as Mode 2 in all respects except

baud rate. The baud rate can be varied at either Timer 1

or 2 overflow rate.

Enhanced TV microcontrollers with

On-Screen Display (OSD)

32

f

clk

UART modes

or

S0CON

S0BUF

1

SFR

16

f

clk

th

th

.

data bit and a stop bit (logic 1).

data bit and a stop bit (logic 1). In fact,

th

data bit, TB8 in S0CON, can be

ADDRESS

9AH

99H

1

6

f

clk

.

th

48

In all four modes, transmission is initiated by any

instruction that uses S0BUF as a destination register.

Reception is initiated in Mode 0 by the condition RI = 0 and

REN = 1. In the other modes, reception is initiated by the

incoming start bit if REN = 1.

18.2

Modes 2 and 3 have a special provision for multiprocessor

communications. In these modes, nine data bits are

received. The 9

The port can be programmed such that when the stop bit

is received, the serial port interrupt will be activated only if

RB8 = 1. This feature is enabled by setting bit SM2 in

S0CON. A way to use this feature in multiprocessor

systems is as follows.

When the master processor wants to transmit a block of

data to one of several slaves, it first sends out an address

byte which identifies the target slave. An address byte

differs from a data byte. The 9

byte and logic 0 in a data byte. With SM2 = 1, no slave will

be interrupted by a data byte reception.

An address byte, however, will interrupt all slaves, so that

each slave can examine the received byte and see if it is

being addressed. The addressed slave will clear its SM2

bit and prepare to receive the data bytes that will follow.

The slaves that were not being addressed leave their

SM2 bits set and carry on the task they were performing.

Bit SM2 has no effect in Mode 0; in Mode 1, it can be used

to check the validity of the stop bit. When receiving in

Mode 1 (if SM2 = 1), the receive interrupt will not be

activated unless a valid stop bit is received.

18.3

This register is implemented twice. Writing to S0BUF

writes to the transmit buffer. Reading from S0BUF reads

from the receive buffer. Only hardware can read from the

transmit buffer and write to the receive buffer.

UART multiprocessor communications

S0BUF registers

th

bit goes into RB8, followed by a stop bit.

SAA567x; SAA569x

th

bit is logic 1 in an address

Objective specification