DEMO9S08JM16 Freescale Semiconductor, DEMO9S08JM16 Datasheet - Page 61

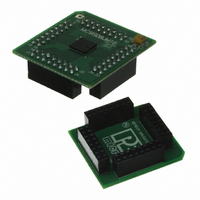

DEMO9S08JM16

Manufacturer Part Number

DEMO9S08JM16

Description

BOARD DEMO FOR JM16 FAMI

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08JM16.pdf

(47 pages)

2.DEMO9S08JM16.pdf

(5 pages)

3.DEMO9S08JM16.pdf

(4 pages)

4.DEMO9S08JM16.pdf

(386 pages)

Specifications of DEMO9S08JM16

Contents

Board with Daughter card, Cable, Documentation, Mini-AB USB Kit

Processor To Be Evaluated

MC9S08JM16

Data Bus Width

8 bit

Interface Type

USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

Flexis - S08JM

Rohs Compliant

Yes

For Use With/related Products

MC9S08JM16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- DEMO9S08JM16 PDF datasheet

- DEMO9S08JM16 PDF datasheet #2

- DEMO9S08JM16 PDF datasheet #3

- DEMO9S08JM16 PDF datasheet #4

- Current page: 61 of 386

- Download datasheet (8Mb)

Chapter 5

Resets, Interrupts, and System Configuration

5.1

This chapter discusses basic reset and interrupt mechanisms and the various sources of reset and interrupts

in the MC9S08JM16 series. Some interrupt sources from peripheral modules are discussed in greater detail

in other chapters of this reference manual. This chapter gathers basic information about all reset and

interrupt sources in one place for easy reference. A few reset and interrupt sources, including the computer

operating properly (COP) watchdog, are not part of on-chip peripheral systems with their own sections but

are part of the system control logic.

5.2

Reset and interrupt features include:

5.3

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset,

most control and status registers are forced to initial values and the program counter is loaded from the

reset vector (0xFFFE:0xFFFF). On-chip peripheral modules are disabled and I/O pins are initially

configured as general-purpose high-impedance inputs with pullup devices disabled. The I bit in the

condition code register (CCR) is set to block maskable interrupts, so the user program has a chance to

initialize the stack pointer (SP) and system control settings. SP is forced to 0x00FF at reset.

The MC9S08JM16 series has eight sources for reset:

Freescale Semiconductor

•

•

•

•

•

•

•

•

•

•

•

Multiple sources of reset for flexible system configuration and reliable operation

Reset status register (SRS) to indicate source of most recent reset

Separate interrupt vectors for each module (reduces polling overhead) (see

Power-on reset (POR)

Low-voltage detect (LVD)

Computer operating properly (COP) timer

Illegal opcode detect (ILOP)

Illegal address detect (ILAD)

Background debug forced reset

External reset pin (RESET)

Clock generator loss of lock and loss of clock reset (LOC)

Introduction

Features

MCU Reset

MC9S08JM16 Series Data Sheet, Rev. 2

Table

5-1)

61

Related parts for DEMO9S08JM16

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: