DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 66

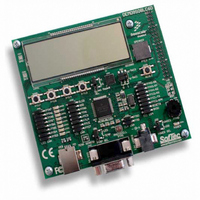

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 66 of 360

- Download datasheet (4Mb)

Chapter 5 Resets, Interrupts, and System Configuration

The interrupt service routine ends with a return-from-interrupt (RTI) instruction which restores the CCR,

A, X, and PC registers to their pre-interrupt values by reading the previously saved information off the

stack.

When two or more interrupts are pending when the I bit is cleared, the highest priority source is serviced

first (see

5.5.1

Figure 5-1

(SP) points at the next available byte location on the stack. The current values of CPU registers are stored

on the stack starting with the low-order byte of the program counter (PCL) and ending with the CCR. After

stacking, the SP points at the next available location on the stack which is the address that is one less than

the address where the CCR was saved. The PC value that is stacked is the address of the instruction in the

main program that would have executed next if the interrupt had not occurred.

When an RTI instruction is executed, these values are recovered from the stack in reverse order. As part of

the RTI sequence, the CPU fills the instruction pipeline by reading three bytes of program information,

starting from the PC address just recovered from the stack.

The status flag causing the interrupt must be acknowledged (cleared) before returning from the ISR.

Typically, the flag should be cleared at the beginning of the ISR so that if another interrupt is generated by

this same source, it will be registered so it can be serviced after completion of the current ISR.

66

Table

shows the contents and organization of a stack frame. Before the interrupt, the stack pointer

Interrupt Stack Frame

For compatibility with the M68HC08, the H register is not automatically

saved and restored. It is good programming practice to push H onto the stack

at the start of the interrupt service routine (ISR) and restore it just before the

RTI that is used to return from the ISR.

5-2).

STACKING

ORDER

UNSTACKING

5

4

3

2

1

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

ORDER

1

2

3

4

5

* High byte (H) of index register is not automatically stacked.

7

INDEX REGISTER (LOW BYTE X)

Figure 5-1. Interrupt Stack Frame

CONDITION CODE REGISTER

PROGRAM COUNTER HIGH

PROGRAM COUNTER LOW

ACCUMULATOR

NOTE

TOWARD HIGHER ADDRESSES

TOWARD LOWER ADDRESSES

*

0

SP AFTER

INTERRUPT STACKING

SP BEFORE

THE INTERRUPT

Freescale Semiconductor

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: