AT91SAM7XC512-CU Atmel, AT91SAM7XC512-CU Datasheet - Page 157

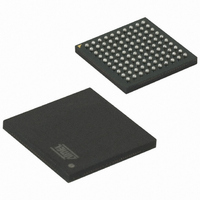

AT91SAM7XC512-CU

Manufacturer Part Number

AT91SAM7XC512-CU

Description

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7XC512-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

AT91SAMx

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

128 KB

Interface Type

MII, SPI, TWI

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-ARM-2M, KSK-AT91SAM7X-PL, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

AT91SAM-ICE, AT91-ISP, AT91SAM7XC-EK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

AT91SAM-ICE - EMULATOR FOR AT91 ARM7/ARM9AT91SAM7XC-EK - KIT EVAL FOR AT91SAM7XC256/128

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 157 of 727

- Download datasheet (11Mb)

Table 21-17. Signal Description List (Continued)

21.3.2

21.3.3

6209F–ATARM–17-Feb-09

Signal Name

TST

PGMEN0

PGMEN1

TCK

TDI

TDO

TMS

Entering Serial Programming Mode

Read/Write Handshake

Function

Test Mode Select

Test Mode Select

Test Mode Select

JTAG TCK

JTAG Test Data In

JTAG Test Data Out

JTAG Test Mode Select

The following algorithm puts the device in Serial Programming Mode:

Note:

Table 21-18. Reset TAP Controller and Go to Select-DR-Scan

The read/write handshake is done by carrying out read/write operations on two registers of the

device that are accessible through the JTAG:

• Apply GND, VDDIO, VDDCORE, VDDFLASH and VDDPLL.

• Apply XIN clock within T

• Wait for T

• Reset the TAP controller clocking 5 TCK pulses with TMS set.

• Shift 0x2 into the IR register (IR is 4 bits long, LSB first) without going through the Run-Test-

• Shift 0x2 into the DR register (DR is 4 bits long, LSB first) without going through the Run-

• Shift 0xC into the IR register (IR is 4 bits long, LSB first) without going through the Run-Test-

Idle state.

Test-Idle state.

Idle state.

After reset, the device is clocked by the internal RC oscillator. Before clearing RDY signal, if an

external clock ( > 32 kHz) is connected to XIN, then the device will switch on the external clock.

Else, XIN input is not considered. An higher frequency on XIN speeds up the programmer

handshake.

TDI

POR_RESET

Xt

X

X

X

X

X

X

AT91SAM7XC512/256/128 Preliminary

.

POR_RESET

JTAG

Test

TMS

1

1

1

1

1

0

1

+ 32(T

Output

Type

Input

Input

Input

Input

Input

Input

TAP Controller State

Test-Logic Reset

Run-Test/Idle

Select-DR-Scan

SCLK

) if an external clock is available.

Active

Level

High

High

High

-

-

-

-

Comments

Must be connected to VDDIO.

Must be connected to VDDIO

Must be connected to VDDIO

Pulled-up input at reset

Pulled-up input at reset

Pulled-up input at reset

157

Related parts for AT91SAM7XC512-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7XC256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet: