EPC8QI100 Altera, EPC8QI100 Datasheet - Page 19

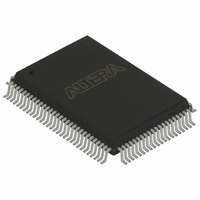

EPC8QI100

Manufacturer Part Number

EPC8QI100

Description

IC CONFIG DEVICE 8MBIT 100-PQFP

Manufacturer

Altera

Series

EPCr

Datasheet

1.EPC8QC100.pdf

(34 pages)

Specifications of EPC8QI100

Programmable Type

In System Programmable

Memory Size

8Mb

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

100-MQFP, 100-PQFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

544-1239

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EPC8QI100

Manufacturer:

ALTERA

Quantity:

10

Company:

Part Number:

EPC8QI100

Manufacturer:

ALTERA

Quantity:

710

Part Number:

EPC8QI100

Manufacturer:

ALTERA

Quantity:

20 000

Company:

Part Number:

EPC8QI100N

Manufacturer:

ALTERA

Quantity:

1 500

Company:

Part Number:

EPC8QI100N

Manufacturer:

ALTERA21

Quantity:

444

Chapter 1: Enhanced Configuration Devices (EPC4, EPC8, and EPC16) Data Sheet

Functional Description

Programmable Configuration Clock

© December 2009 Altera Corporation

f

Table 1–6. Stratix Compression Ratios

The configuration clock (DCLK) speed is user programmable. One of two clock sources

can be used to synthesize the configuration clock; a programmable oscillator or an

external clock input pin (EXCLK). The configuration clock frequency can be further

synthesized using the clock divider circuitry. This clock can be divided by the N

counter to generate your DCLK output. The N divider supports all integer dividers

between 1 and 16, as well as a 1.5 divider and a 2.5 divider. The duty cycle for all clock

divisions other than non-integer divisions is 50% (for the non-integer dividers, the

duty cycle will not be 50%). Refer to

divider unit.

Figure 1–5. Clock Divider Unit

The DCLK frequency is limited by the maximum DCLK frequency the FPGA supports.

The maximum DCLK input frequency supported by the FGPA is specified in the

appropriate FPGA family chapter in the

Logic Utilization

Compression Ratio

% Size Reduction

Note to

(1) These numbers are preliminary. They are intended to serve as a guideline, not a specification.

Table

(Up to 100 MHz)

External Clock

1–6:

Item

10 MHz

33 MHz

50 MHz

66 MHz

Internal Oscillator

(Note 1)

Figure 1–5

Configuration Device

Minimum

Configuration

98%

47%

1.9

Clock Divider Unit

for a block diagram of the clock

Configuration Handbook (Complete Two-Volume Set)

Divide

by N

Handbook.

Average

64%

57%

2.3

DCLK

1–19