EPC8QI100 Altera, EPC8QI100 Datasheet - Page 27

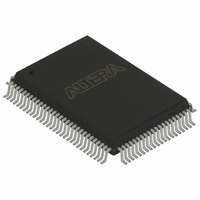

EPC8QI100

Manufacturer Part Number

EPC8QI100

Description

IC CONFIG DEVICE 8MBIT 100-PQFP

Manufacturer

Altera

Series

EPCr

Datasheet

1.EPC8QC100.pdf

(34 pages)

Specifications of EPC8QI100

Programmable Type

In System Programmable

Memory Size

8Mb

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

100-MQFP, 100-PQFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

544-1239

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EPC8QI100

Manufacturer:

ALTERA

Quantity:

10

Company:

Part Number:

EPC8QI100

Manufacturer:

ALTERA

Quantity:

710

Part Number:

EPC8QI100

Manufacturer:

ALTERA

Quantity:

20 000

Company:

Part Number:

EPC8QI100N

Manufacturer:

ALTERA

Quantity:

1 500

Company:

Part Number:

EPC8QI100N

Manufacturer:

ALTERA21

Quantity:

444

Chapter 1: Enhanced Configuration Devices (EPC4, EPC8, and EPC16) Data Sheet

Programming and Configuration File Support

Table 1–11. Enhanced Configuration Device JTAG Instructions (Part 2 of 2)

© December 2009 Altera Corporation

INIT_CONF

PENDCFG

Note to

(1) Enhanced configuration device instruction register length is 10 and boundary scan length is 174.

JTAG Instruction

Table

1–11:

f

00 0110 0001

00 0110 0101

For more information about the enhanced configuration device JTAG support, refer to

the BSDL files provided at the Altera website.

Enhanced configuration devices can also be programmed by third-party flash

programmers or on-board processors using the external flash interface. Programming

files (.pof) can be converted to an Intel HEX format file (.hexout) using the Quartus II

Convert Programming Files utility, for use with the programmers or processors.

You can also program the enhanced configuration devices using the Quartus II

software, the Altera Programming Unit (APU), and the appropriate configuration

device programming adapter.

with each enhanced configuration device.

Table 1–12. Programming Adapters

EPC16

EPC8

EPC4

OPCODE

Device

This function initiates the FPGA re-configuration process by pulsing the

nINIT_CONF pin low, which is connected to the FPGA nCONFIG pin. After

this instruction is updated, the nINIT_CONF pin is pulsed low when the JTAG

state machine enters Run-Test/Idle state. The nINIT_CONF pin is then

released and nCONFIG is pulled high by the resistor after the JTAG state

machine goes out of Run-Test/Idle state. The FPGA configuration starts after

nCONFIG goes high. As a result, the FPGA is configured with the new

configuration data stored in flash via ISP. This function can be added to your

programming file (

Initiate configuration after programming option in the Programmer options

window (Options menu).

This optional function can be used to hold the nINIT_CONF pin low during

JTAG-based ISP of the enhanced configuration device. This feature is useful

when the external flash interface is controlled by an external FPGA/processor.

This function prevents contention on the flash pins when both the controller and

external device try to access the flash simultaneously. Before the enhanced

configuration device’s controller can access the flash memory, the external

FPGA/processor needs to tri-state its interface to flash.This can be ensured by

resetting the FPGA using the nINIT_CONF, which drives the nCONFIG pin and

keeps the external FPGA/processor in the “reset” state. The nINIT_CONF pin is

released when the initiate configuration (INIT_CONF) JTAG instruction is

issued.

88-pin UFBGA

100-pin PQFP

100-pin PQFP

100-pin PQFP

Table 1–12

.pof , .jam, .jbc) in the Quartus II software by enabling the

Package

lists which programming adapter to use

(Note 1)

Description

Configuration Handbook (Complete Two-Volume Set)

PLMUEPC-88

PLMQEPC-100

PLMQEPC-100

PLMQEPC-100

Adapter

1–27