MC908AZ60ACFUER Freescale Semiconductor, MC908AZ60ACFUER Datasheet - Page 131

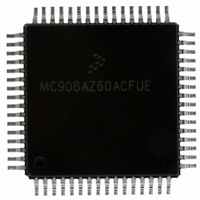

MC908AZ60ACFUER

Manufacturer Part Number

MC908AZ60ACFUER

Description

IC MCU 60K FLASH 8.4MHZ 64-QFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908AZ60ACFUER.pdf

(414 pages)

Specifications of MC908AZ60ACFUER

Core Processor

HC08

Core Size

8-Bit

Speed

8.4MHz

Connectivity

CAN, SCI, SPI

Peripherals

LVD, POR, PWM

Number Of I /o

52

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Eeprom Size

1K x 8

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 15x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

64-QFP

Processor Series

HC08AZ

Core

HC08

Data Bus Width

8 bit

Data Ram Size

2 KB

Interface Type

SCI, SPI

Maximum Clock Frequency

8.4 MHz

Number Of Programmable I/os

52

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, M68CBL05CE, ZK-HC08AX-A, M68EM08AS/AZ60AE

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit, 15 Channel

Controller Family/series

HC08

No. Of I/o's

52

Eeprom Memory Size

1KB

Ram Memory Size

2KB

Cpu Speed

8MHz

No. Of Timers

2

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

MC908AZ60ACFUERTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AZ60ACFUER

Manufacturer:

FREESCALE

Quantity:

5 560

Company:

Part Number:

MC908AZ60ACFUER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 131 of 414

- Download datasheet (5Mb)

10.3.2.3 Manual and Automatic PLL Bandwidth Modes

The PLL can change the bandwidth or operational mode of the loop filter manually or automatically.

In automatic bandwidth control mode (AUTO = 1), the lock detector automatically switches between

acquisition and tracking modes. Automatic bandwidth control mode also is used to determine when the

VCO clock, CGMVCLK, is safe to use as the source for the base clock, CGMOUT. See

Bandwidth Control

CPU interrupt request and then check the LOCK bit. If CPU interrupts are disabled, software can poll the

LOCK bit continuously (during PLL startup, usually) or at periodic intervals. In either case, when the LOCK

bit is set, the VCO clock is safe to use as the source for the base clock. See

Circuit. If the VCO is selected as the source for the base clock and the LOCK bit is clear, the PLL has

suffered a severe noise hit and the software must take appropriate action, depending on the application.

See

These conditions apply when the PLL is in automatic bandwidth control mode:

The PLL also can operate in manual mode (AUTO = 0). Manual mode is used by systems that do not

require an indicator of the lock condition for proper operation. Such systems typically operate well below

f

Freescale Semiconductor

busmax

•

•

•

•

•

•

•

•

•

•

10.6

The ACQ bit (See

the filter. See

The ACQ bit is set when the VCO frequency is within a certain tolerance, Δ

the VCO frequency is out of a certain tolerance, Δ

The LOCK bit is a read-only indicator of the locked state of the PLL.

The LOCK bit is set when the VCO frequency is within a certain tolerance, Δ

when the VCO frequency is out of a certain tolerance, Δ

Specifications.

CPU interrupts can occur if enabled (PLLIE = 1) when the PLL’s lock condition changes, toggling

the LOCK bit. See

ACQ is a writable control bit that controls the mode of the filter. Before turning on the PLL in manual

mode, the ACQ bit must be clear.

Before entering tracking mode (ACQ = 1), software must wait a given time, t

Electrical

(PCTL).

Software must wait a given time, t

clock source to CGMOUT (BCS = 1).

The LOCK bit is disabled.

CPU interrupts from the CGM are disabled.

and require fast startup. The following conditions apply when in manual mode:

Interrupts.

Specifications), after turning on the PLL by setting PLLON in the PLL control register

MC68HC908AZ60A • MC68HC908AS60A • MC68HC908AS60E Data Sheet, Rev. 6

Register. If PLL CPU interrupt requests are enabled, the software can wait for a PLL

10.3.2.2 Acquisition and Tracking

10.5.2 PLL Bandwidth Control

10.5.1 PLL Control

al

, after entering tracking mode before selecting the PLL as the

Register.

Modes.

Register.) is a read-only indicator of the mode of

unt

. See

unl

Chapter 28 Electrical

. See

Chapter 28 Electrical

10.3.3 Base Clock Selector

trk

, and is cleared when

acq

Lock

Functional Description

(see

Specifications.

, and is cleared

10.5.2 PLL

Chapter 28

131

Related parts for MC908AZ60ACFUER

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: