MC908AZ60ACFUER Freescale Semiconductor, MC908AZ60ACFUER Datasheet - Page 239

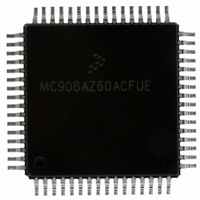

MC908AZ60ACFUER

Manufacturer Part Number

MC908AZ60ACFUER

Description

IC MCU 60K FLASH 8.4MHZ 64-QFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908AZ60ACFUER.pdf

(414 pages)

Specifications of MC908AZ60ACFUER

Core Processor

HC08

Core Size

8-Bit

Speed

8.4MHz

Connectivity

CAN, SCI, SPI

Peripherals

LVD, POR, PWM

Number Of I /o

52

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Eeprom Size

1K x 8

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 15x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

64-QFP

Processor Series

HC08AZ

Core

HC08

Data Bus Width

8 bit

Data Ram Size

2 KB

Interface Type

SCI, SPI

Maximum Clock Frequency

8.4 MHz

Number Of Programmable I/os

52

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, M68CBL05CE, ZK-HC08AX-A, M68EM08AS/AZ60AE

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit, 15 Channel

Controller Family/series

HC08

No. Of I/o's

52

Eeprom Memory Size

1KB

Ram Memory Size

2KB

Cpu Speed

8MHz

No. Of Timers

2

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

MC908AZ60ACFUERTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AZ60ACFUER

Manufacturer:

FREESCALE

Quantity:

5 560

Company:

Part Number:

MC908AZ60ACFUER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 239 of 414

- Download datasheet (5Mb)

CHxF — Channel x Flag Bit

CHxIE — Channel x Interrupt Enable Bit

MSxB — Mode Select Bit B

MSxA — Mode Select Bit A

Freescale Semiconductor

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on

the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the

TIMB counter registers matches the value in the TIMB channel x registers.

When CHxIE = 1, clear CHxF by reading TIMB channel x status and control register with CHxF set,

and then writing a logic 0 to CHxF. If another interrupt request occurs before the clearing sequence is

complete, then writing logic 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due

to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a logic 1 to CHxF has no effect.

This read/write bit enables TIMB CPU interrupts on channel x.

Reset clears the CHxIE bit.

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TIMB

channel 0.

Setting MS0B disables the channel 1 status and control register and reverts TBCH1 to

general-purpose I/O.

Reset clears the MSxB bit.

When ELSxB:A ≠ 00, this read/write bit selects either input capture operation or unbuffered output

compare/PWM operation (see

1 = Input capture or output compare on channel x

0 = No input capture or output compare on channel x

1 = Channel x CPU interrupt requests enabled

0 = Channel x CPU interrupt requests disabled

1 = Buffered output compare/PWM operation enabled

0 = Buffered output compare/PWM operation disabled

1 = Unbuffered output compare/PWM operation

0 = Input capture operation

Register Name and Address

Register Name and Address

Figure 20-7. TIMB Channel Status and Control Registers (TBSC0–TBSC1)

Reset:

Reset:

Read:

Read:

Write:

Write:

MC68HC908AZ60A • MC68HC908AS60A • MC68HC908AS60E Data Sheet, Rev. 6

CH0F

CH1F

Bit 7

Bit 7

R

0

0

0

0

= Reserved

CH0IE

CH1IE

Table

6

0

6

0

TBSC0 — $0045

TBSC1 — $0048

20-2).

MS0B

5

0

5

0

R

0

MS0A

MS1A

4

0

4

0

ELS0B

ELS1B

3

0

3

0

ELS0A

ELS1A

2

0

2

0

TOV0

TOV1

1

0

1

0

CH0MAX

CH1MAX

Bit 0

Bit 0

0

0

I/O Registers

239

Related parts for MC908AZ60ACFUER

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: