LIS302DLTR STMicroelectronics, LIS302DLTR Datasheet - Page 13

LIS302DLTR

Manufacturer Part Number

LIS302DLTR

Description

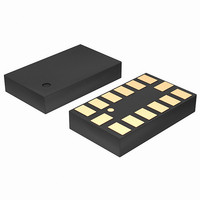

ACCELEROMETER 3AXIS MEMS 14-LGA

Manufacturer

STMicroelectronics

Datasheet

1.STEVAL-MKI006V1.pdf

(42 pages)

Specifications of LIS302DLTR

Featured Product

STM32 Cortex-M3 Companion Products

Axis

X, Y, Z

Acceleration Range

±2.3g, 9.2g

Sensitivity

18mg/digit, 72mg/digit

Voltage - Supply

2.16 V ~ 3.6 V

Output Type

Digital

Bandwidth

100Hz ~ 400Hz Selectable

Interface

I²C, SPI

Mounting Type

Surface Mount

Package / Case

14-LGA

Sensing Axis

X, Y, Z

Acceleration

2 g, 8 g

Digital Output - Number Of Bits

8 bit

Supply Voltage (max)

3.6 V

Supply Voltage (min)

2.16 V

Supply Current

0.3 mA

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Digital Output - Bus Interface

I2C, SPI

Shutdown

Yes

For Use With

497-9047 - BOARD DEMO ACCELEROMETER DIL24497-8373 - BOARD EVAL EXTENSION SN250497-8204 - BOARD ADAPTER LIS302SG DIL24497-8203 - BOARD DEMO LIS302SG497-6404 - BOARD EVAL SPZB260 MOD FOR STR9497-6342 - BOARD EVALUATION FOR LIS302DL497-6246 - BOARD EVAL ACCELEROM LIS302ALK497-6227 - BOARD ADAPTER 20DIP LIS3LV02DL497-6226 - BOARD EVAL ACCELEROM LIS3LV02DL

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-5911-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LIS302DLTR

Manufacturer:

ST

Quantity:

1 056

Part Number:

LIS302DLTR

Manufacturer:

ST

Quantity:

20 000

Company:

Part Number:

LIS302DLTR8

Manufacturer:

SONY

Quantity:

26

Part Number:

LIS302DLTR8

Manufacturer:

ST

Quantity:

20 000

LIS302DL

1. Data based on standard I

2. A device must internally provide an hold time of at least 300ns for the SDA signal (referred to VIHmin of the SCL signal) to

3. Cb = total capacitance of one bus line, in pF

4. Measurement points are done at 0.2·Vdd_IO and 0.8·Vdd_IO, for both port

t

t

SCL

r(SDA)

SDA

f(SDA)

bridge the undefined region of the falling edge of SCL

t

Symbol

t

t

t

w(SP:SR)

w(SCLH)

t

w(SCLL)

t

su(SDA)

t

f

h(SDA)

t

su(SR)

su(SP)

(SCL)

h(ST)

t

t

t

r(SCL)

f(SCL)

f(SDA)

2.3.2

Subject to general operating conditions for Vdd and Top.

Table 6.

Figure 4.

t

h(ST)

SCL clock frequency

SCL clock low time

SCL clock high time

SDA setup time

SDA data hold time

SDA and SCL rise time

SDA and SCL fall time

START condition hold time

Repeated START condition

setup time

STOP condition setup time

Bus free time between STOP

and START condition

START

t

w(SCLL)

t

I

r(SDA)

2

2

C - inter IC control interface

Parameter

C protocol requirement, not tested in production

I

I

2

2

C Slave timing diagram

C slave timing values

t

w(SCLH)

t

su(SDA)

t

r(SCL)

I

2

C standard mode

Min

250

4.7

4.0

4.7

4.7

0

0

4

4

t

f(SCL)

t

h(SDA)

(4)

3.45

1000

Max

Mechanical and electrical specifications

100

300

(2)

(1)

20 + 0.1C

20 + 0.1C

Min

100

1.3

0.6

0.6

0.6

0.6

1.3

I

0

0

2

t

C fast mode

su(SR)

b

b

t

(3)

(3)

su(SP)

t

w(SP:SR)

0.9

Max

400

300

300

(1)

REPEATED

(2)

START

STOP

START

Unit

13/42

KHz

µs

ns

µs

ns

µs