LIS302DLTR STMicroelectronics, LIS302DLTR Datasheet - Page 19

LIS302DLTR

Manufacturer Part Number

LIS302DLTR

Description

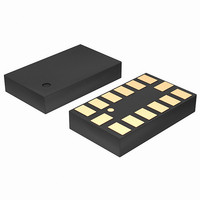

ACCELEROMETER 3AXIS MEMS 14-LGA

Manufacturer

STMicroelectronics

Datasheet

1.STEVAL-MKI006V1.pdf

(42 pages)

Specifications of LIS302DLTR

Featured Product

STM32 Cortex-M3 Companion Products

Axis

X, Y, Z

Acceleration Range

±2.3g, 9.2g

Sensitivity

18mg/digit, 72mg/digit

Voltage - Supply

2.16 V ~ 3.6 V

Output Type

Digital

Bandwidth

100Hz ~ 400Hz Selectable

Interface

I²C, SPI

Mounting Type

Surface Mount

Package / Case

14-LGA

Sensing Axis

X, Y, Z

Acceleration

2 g, 8 g

Digital Output - Number Of Bits

8 bit

Supply Voltage (max)

3.6 V

Supply Voltage (min)

2.16 V

Supply Current

0.3 mA

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Digital Output - Bus Interface

I2C, SPI

Shutdown

Yes

For Use With

497-9047 - BOARD DEMO ACCELEROMETER DIL24497-8373 - BOARD EVAL EXTENSION SN250497-8204 - BOARD ADAPTER LIS302SG DIL24497-8203 - BOARD DEMO LIS302SG497-6404 - BOARD EVAL SPZB260 MOD FOR STR9497-6342 - BOARD EVALUATION FOR LIS302DL497-6246 - BOARD EVAL ACCELEROM LIS302ALK497-6227 - BOARD ADAPTER 20DIP LIS3LV02DL497-6226 - BOARD EVAL ACCELEROM LIS3LV02DL

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-5911-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LIS302DLTR

Manufacturer:

ST

Quantity:

1 056

Part Number:

LIS302DLTR

Manufacturer:

ST

Quantity:

20 000

Company:

Part Number:

LIS302DLTR8

Manufacturer:

SONY

Quantity:

26

Part Number:

LIS302DLTR8

Manufacturer:

ST

Quantity:

20 000

LIS302DL

5.1.1

I

The transaction on the bus is started through a START (ST) signal. A START condition is

defined as a HIGH to LOW transition on the data line while the SCL line is held HIGH. After

this has been transmitted by the Master, the bus is considered busy. The next byte of data

transmitted after the start condition contains the address of the slave in the first 7 bits and

the eighth bit tells whether the Master is receiving data from the slave or transmitting data to

the slave. When an address is sent, each device in the system compares the first seven bits

after a start condition with its address. If they match, the device considers itself addressed

by the Master.

The Slave ADdress (SAD) associated to the LIS302DL is 001110xb. SDO pad can be used

to modify less significant bit of the device address. If SDO pad is connected to voltage

supply LSb is ‘1’ (address 0011101b) else if SDO pad is connected to ground LSb value is

‘0’ (address 0011100b). This solution permits to connect and address two different

accelerometer to the same I

Data transfer with acknowledge is mandatory. The transmitter must release the SDA line

during the acknowledge pulse. The receiver must then pull the data line LOW so that it

remains stable low during the HIGH period of the acknowledge clock pulse. A receiver which

has been addressed is obliged to generate an acknowledge after each byte of data has

been received.

The I

protocol must be adhered to. After the start condition (ST) a salve address is sent, once a

slave acknowledge (SAK) has been returned, a 8-bit sub-address will be transmitted: the 7

LSb represent the actual register address while the MSB enables address auto increment. If

the MSb of the SUB field is 1, the SUB (register address) will be automatically incremented

to allow multiple data read/write.

The slave address is completed with a Read/Write bit. If the bit was ‘1’ (Read), a repeated

START (SR) condition will have to be issued after the two sub-address bytes; if the bit is ‘0’

(Write) the Master will transmit to the slave with direction unchanged.

the SAD+Read/Write bit pattern is composed, listing all the possible configurations.

Table 10.

Table 11.

Table 12.

2

Master

C operation

Slave

Master

Slave

Command

2

C embedded inside the LIS302DL behaves like a slave device and the following

Read

Read

Write

Write

ST

SAD+Read/Write patterns

Transfer when master is writing one byte to slave

Transfer when master is writing multiple bytes to slave

ST

SAD + W

SAD[6:1]

001110

001110

001110

001110

SAD + W

2

C lines.

SAK

SAK

SUB

SAD[0] = SDO

0

0

1

1

SAK

SUB

DATA

SAK

R/W

SAK

0

1

0

1

DATA

Table 10

00111001 (39h)

00111000 (38h)

00111011 (3Bh)

00111010 (3Ah)

DATA

Digital interfaces

SAD+R/W

SAK

explains how

SAK

SP

19/42

SP