SAA7385GP Philips Semiconductors, SAA7385GP Datasheet - Page 28

SAA7385GP

Manufacturer Part Number

SAA7385GP

Description

Error correction and host interface IC for CD-ROM SEQUOIA

Manufacturer

Philips Semiconductors

Datasheet

1.SAA7385GP.pdf

(64 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SAA7385GP

Manufacturer:

PHILIPS

Quantity:

10 680

Philips Semiconductors

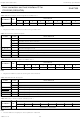

Table 31 BRGSEL field description

Table 32 UART special control register: 0xF09E; note 1

Note

1. Register 0xF09E allows the 80C32 UART clock to be derived from 16.945 MHz. This external UART clock is required

Table 33 UARTCTL field description

1996 Jun 19

ICESEL1 to 0

INVQ

INVSUBC

EVENPAR

LOCK

C_34_16

DIVIDE5 to 0

UARTCNT

EXTUART

MNEMONIC

Error correction and host interface IC for

CD-ROM (SEQUOIA)

UARTCTL

for reliable operation of the UART if the 80C32 is used for other functions during the transfer.

FIELD

FIELD

LOGIC

LOGIC

R/W

R/W

00

01

10

11

0

1

0

1

EXTUART UARTCNT

62.5 kbaud transfer rate

187.5 kbaud transfer rate

not specified

inverts all Q-channel information if set

inverts all sub-code information if set

selects even parity for S2B UART is set

read only information; indicates clock synthesizer is stable (after reset) and it is ready to set

C_34_16

once LOCK is HIGH, asserting this bit engages the clock doubler

value 0 produces a 0.264 MHz clock and 58 produces a 2.82 MHz clock for the UART; this is

the maximum accepted by the 80C32, a smaller number is required for guaranteed

operation e.g. 15

normal UART data input sampled by the external clock

select a UART data input sampled by the clock from the internal counter

use external UART clock; disables internal clock

switch external UART clock input from pin to this internal counter

31.25 kbaud transfer rate

7

6

DIVIDE5

5

28

DIVIDE4

DESCRIPTION

DESCRIPTION

DATA BYTE

4

DIVIDE3

3

DIVIDE2

2

Preliminary specification

DIVIDE1

1

SAA7385

DIVIDE0

0