SAA7385GP Philips Semiconductors, SAA7385GP Datasheet - Page 35

SAA7385GP

Manufacturer Part Number

SAA7385GP

Description

Error correction and host interface IC for CD-ROM SEQUOIA

Manufacturer

Philips Semiconductors

Datasheet

1.SAA7385GP.pdf

(64 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SAA7385GP

Manufacturer:

PHILIPS

Quantity:

10 680

Philips Semiconductors

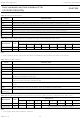

Table 49 Front-end frame number: 0xF0E4, F0E5

This register allows the front-end frame number counter to be read and reloaded. The counter associated with these

registers is loaded after the most significant byte is written; the least significant byte must be written first to ensure that

the counter is loaded correctly. If a DRAM access is in progress that uses the address from the counter, the update will

be delayed until the access is completed. This counter is cleared on reset or when the last frame, as specified by

LASTFRM, is filled. Therefore, this register should only be loaded if a non-zero start frame number is required. The frame

counter is automatically cleared at the end of the frame buffer memory and thus multiple passes of a non-zero start

address will require a re-load for each pass; it is not practical to do this in real-time.

Table 50 Last frame number for storage: 0xF0F8, F0F9

These registers are used by the buffer manager to set the top of frame storage memory (wrap point). Any memory past

this point is available for general usage by the microcontroller. The outputs of the registers are used directly to control

DRAM access cycles, and will affect any current DRAM cycle in progress. Both the SCSI address counter and the

front-end frame address counter use this value to determine the correct location to clear their respective frame counters.

11.2

The microcontroller interface allows the microcontroller to read or write any register or the frame store memory. Frame

and offset registers are used to update the counters after the most significant byte has been loaded. Frame store memory

is addressed using a frame number register controller by the microcontroller. Logic is provided to allow the frame number

of the last complete frame received (LSTCMPFM) from the front-end to be read by the microcontroller for the purpose of

setting the microcontroller frame address. Memory beyond the last frame number is available to the microcontroller using

the microcontroller bottom 32 kbyte located at 0x0000 to 0x7FFF. The 4 kbyte segment at 0x8000 to 0x8FFF is used to

address the current frame memory. Also, the next frame may be accessed at 0x9000 to 0x9FFF, and the current frame

plus 2 may be accessed at 0xA000 to 0xAFFF. A page register is provided to allow the microcontroller to address the

complete memory range in 32 kbyte pages. All microcontroller accesses to memory are single byte read or write cycles.

All microcontroller accesses to memory will generate a wait state. If no other accesses to memory are in progress then

a minimum wait state cycle will be generated. If, however, other cycles are in progress then the microcontroller is forced

to wait until the lower priority access cycles finish and any high priority access cycles are completed. The worst case wait

is four complete access cycles; a total of 20 clock cycles in byte mode and 32 cycles in nibble mode.

1996 Jun 19

MNEMONIC

MNEMONIC

Error correction and host interface IC for

CD-ROM (SEQUOIA)

LASTFRM

LASTFRM

FEFRM#

FEFRM#

Microcontroller to buffer manager interface

R/W

R/W

R/W

R/W

R/W

R/W

NUM7

NUM7

7

7

NUM6

NUM6

6

6

NUM5

NUM5

5

5

35

NUM4

NUM4

4

4

DATA BYTE

DATA BYTE

NUM3

NUM3

3

3

NUM2

NUM2

2

2

Preliminary specification

NUM1

NUM1

1

1

SAA7385

NUM0

NUM8

NUM0

NUM8

0

0