SAA7385GP Philips Semiconductors, SAA7385GP Datasheet - Page 34

SAA7385GP

Manufacturer Part Number

SAA7385GP

Description

Error correction and host interface IC for CD-ROM SEQUOIA

Manufacturer

Philips Semiconductors

Datasheet

1.SAA7385GP.pdf

(64 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SAA7385GP

Manufacturer:

PHILIPS

Quantity:

10 680

Philips Semiconductors

11 BUFFER MANAGER

11.1

The buffer manager interface to the front-end is write only with no handshaking. The front-end passes one byte of data

and a write strobe to the buffer manager; this byte will be one of five types of data (see Table 47). The data byte is latched

and the interface is given the highest priority thus no wait signal is required. The other signals passed from the front-end

logic are an end-of-frame strobe (which is the same as the status byte write strobe), a software-generated reset pulse

(used to reset the front-end counters), and a reset pulse for the Q-channel and sub-code offset counters.

The buffer manager provides the remainder of the logic to write the data into the RAM and keep track of the frame

addresses and offset addresses. This logic consists of a 12-bit frame offset counter FEOFF, for data and an 9-bit frame

counter; this is a relative frame number and is not related to the CD-ROM frame number. Offset counters are also

provided for the four other types of data. The other offset address generators are based on fixed addresses, and they

will be loaded with the start address at the beginning of each frame. The five types of data from the front-end are loaded

into the frame map as shown in Table 47.

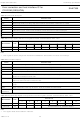

Table 47 Data types from the front-end

Initially the front-end frame counter and all of the offset counters are cleared by reset or loaded with the contents of

FEFRM# when the last frame as specified by LASTFRM is filled; therefore FEFRM# should be loaded with the required

starting frame number. The data frame offset counter, FEFRMOFF, may be loaded for test purposes, but is cleared at

the end of each frame.

LASTFRM establishes the limit of the frame memory. This register should be loaded with the required number of frames;

the amount of memory used is 3 kbytes times the number of frames. The front-end frame address counter uses this value

to determine the correct location to clear the counter.

Once the data load process starts, the offset counter (FEFRMOFF) increments after each byte is written into memory.

This process continues until an end of frame signal is received from the front-end logic. If an error occurs and the offset

counter increments past the maximum 2352, an interrupt will be issued to the microcontroller.

Table 48 Front-end frame offset: 0xF0E2, F0E3

This register allows the front-end frame offset counter to be read and reloaded. The counter associated with these

registers is loaded after the most significant byte is written; the least significant byte must be written first to ensure that

the counter is loaded correctly. If a DRAM access is in progress that uses the address from the counter, the update will

be delayed until the access is complete. This counter is cleared on reset or after each frame is loaded into buffer memory.

Therefore, this register should not be loaded during normal operation.

1996 Jun 19

MNEMONIC

FEFRMOFF

FEFRMOFF

Error correction and host interface IC for

CD-ROM (SEQUOIA)

START

0xBDE

0x9A0

0x000

0x930

0x940

Front-end to buffer manager interface

R/W

R/W

R/W

0xBDE

0xAC5

0x92F

0x93F

0x99F

END

7

LENGTH

0x930

0x010

0x060

0x126

0x001

6

header, data and parity

Q-channel

sub-channel

error flags

status byte

5

34

OFFSET7 to OFFSET0

4

DATA BYTE

3

DATA TYPE

OFFSET11 to OFFSET8

2

Preliminary specification

1

SAA7385

0