SAA7385GP Philips Semiconductors, SAA7385GP Datasheet - Page 31

SAA7385GP

Manufacturer Part Number

SAA7385GP

Description

Error correction and host interface IC for CD-ROM SEQUOIA

Manufacturer

Philips Semiconductors

Datasheet

1.SAA7385GP.pdf

(64 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SAA7385GP

Manufacturer:

PHILIPS

Quantity:

10 680

Philips Semiconductors

10 FRONT-END

This Chapter explains the information of the front-end circuitry.

10.1

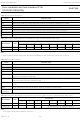

Table 40 Header mode and MSF from block decoder: 0xF092, F093, F09A and F09B

These registers contain the mode, minute, second and frame information from the header when in data mode. This data

is valid whenever the HDDRDY bit in the RDDSTAT register is set. In audio mode, the MSF address is taken from the

Q-channel information.

Table 41 Q-channel information: 0xF0A9, F0AA, F0AB, F0B1 and F0B2

These registers contain the information taken from the raw sub-channel information from the CD decoder. Due to the fact

that this data has not had any error correction applied to it, it is necessary to perform a CRC check for validity. Twelve

bytes of Q-channel information are assembled from each sector of data; the last two bytes contain the CRC parity.

Therefore the validity of the contents of these registers can only be determined after the last bit has been loaded and

checked.

Table 42 Times from QCHRDY to BADQ (RDDSTAT)

1996 Jun 19

MNEMONIC

MNEMONIC

Error correction and host interface IC for

CD-ROM (SEQUOIA)

MODE

RDMD

RDMN

RDFM

FRMS

RDSC

SECS

RDTK

MINS

Minute Second Frame (MSF) addressing and header information

SPEED

n = 1

n = 2

n = 4

n = 6

n = 8

R/W

R/W

R

R

R

R

R

R

R

R

R

7

7

TIME ( s)

6

6

2177

1089

545

363

273

5

5

SECONDS7 to SECONDS0

MINUTES7 to MINUTES0

31

ABSFRM7 to ABSFRM0

ABSSEC7 to ABSSEC0

ABSMIN7 to ABSMIN0

FRAME7 to FRAME0

TRACK7 to TRACK0

MODE7 to MODE0

MODE7 to MODE0

For example, at the n = 4 data rate, the BADQ flag

(in RDDSTAT) should be checked 545 s after the

QFRMRDY interrupt (from RDDSTAT) is asserted.

If BADQ is LOW then the contents of the Q-channel

registers are valid; otherwise the CRC check failed and the

Q-channel information may be incorrect. If the data clock

is running (ECMD LOW or ENABRED HIGH) then BADQ

will be valid until the end of the sector; otherwise BADQ is

valid until the end of the next Q frame.

4

4

DATA BYTE

DATA BYTE

3

3

2

2

Preliminary specification

1

1

SAA7385

0

0