SAA7385GP Philips Semiconductors, SAA7385GP Datasheet - Page 32

SAA7385GP

Manufacturer Part Number

SAA7385GP

Description

Error correction and host interface IC for CD-ROM SEQUOIA

Manufacturer

Philips Semiconductors

Datasheet

1.SAA7385GP.pdf

(64 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SAA7385GP

Manufacturer:

PHILIPS

Quantity:

10 680

Philips Semiconductors

10.2

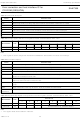

Table 43 Front-end control: 0xF0BB; note 1

Note

1. Register 0xF0BB controls the front-end of the SAA7385. The naming convention used here is similar to that used in

Table 44 FECTL field description

1996 Jun 19

ECMD

SYNASYN

AUDMODE

ENABRED

RWMD

BREAK

RSMD

SIM_EOF

MNEMONIC

Error correction and host interface IC for

CD-ROM (SEQUOIA)

FECTL

the block decoders.

FIELD

Front-end status and control

R/W

R/W SIM_EOF

LOGIC

0

1

0

1

0

1

0

1

Data is shifted in and stored when the next synchronization pattern is detected;

(SYNASYN = 1 and AUDMODE = 0).

(SYNASYN = 1).

Synchronous/asynchronous selection; this controls the method by which data is started and

stopped by the block decoder, only operates in data mode.

Causes a ‘panic stop’. A partial frame will reside in current and subsequent buffers unless

SIM_EOF is set then cleared; (ECMD = 1).

Data is started and stopped on frame boundaries (on synchronization patterns).

Data mode. Cleared on reset.

Audio mode, where the bit clock is shifted to accommodate EIAJ format. HQRDY in

INTRFLG follows HDRRDY in data mode and QFRMDRY in audio mode.

Enable red book to data path; while in audio mode, this is equivalent to ECMD in the data

mode. No asynchronous stop is provided in the audio mode.

Data flow will stop when the next F1 C-flag is detected. Cleared on a reset condition.

Red book data is input to buffer after the detection of the next F1 C-flag.

This must be pulsed HIGH then LOW every 212 ms to prevent the watch-dog timer from

resetting the SAA7385 and the drive. The length of the reset pulse is 967 s. If RWMD is set,

the watch-dog timer is disabled.

When set, the S2B UART transmitter output is held HIGH.

When the pulse is HIGH then LOW, the block decoder begins to search for a synchronization

pattern in the data bitstream. Once a synchronization pattern is found, MODE, MINS, SECS,

and FRMS become valid.

This provides a firmware reset to the frame sequencer and parts of the buffer manager.

This would be required if an asynchronous stop of the data stream occurs. Pulsing this HIGH

then LOW resets all counters and establishes a ‘beginning of frame’ state. DCOACT in

RDDSTAT must be LOW to allow SIM_EOF to have any effect. If SIM_EOF is set, no data or

sub-code is stored in the buffer.

Data flow stop just before next synchronization pattern. ECMD is set on a reset condition;

7

RSMD

6

BREAK

5

32

RWMD

4

DATA BYTE

DESCRIPTION

ENABRED AUDMODE SYNASYN

3

2

Preliminary specification

1

SAA7385

ECMD

0