MC9S08AC16CFJE Freescale Semiconductor, MC9S08AC16CFJE Datasheet - Page 110

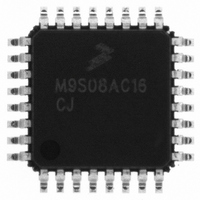

MC9S08AC16CFJE

Manufacturer Part Number

MC9S08AC16CFJE

Description

IC MCU 8BIT 16K FLASH 32-LQFP

Manufacturer

Freescale Semiconductor

Series

HCS08r

Specifications of MC9S08AC16CFJE

Core Processor

HCS08

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

22

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 6x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

Processor Series

S08AC

Core

HCS08

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

SCI/SPI

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

22

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWS08

Development Tools By Supplier

DEMO9S08AC60E, DEMOACEX, DEMOACKIT, DCF51AC256, DC9S08AC128, DC9S08AC16, DC9S08AC60, DEMO51AC256KIT

Minimum Operating Temperature

- 40 C

On-chip Adc

6-ch x 10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08AC16CFJE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC9S08AC16CFJER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 110 of 336

- Download datasheet (7Mb)

Chapter 7 Central Processor Unit (S08CPUV2)

7.3

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status

and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit

binary address can uniquely identify any memory location. This arrangement means that the same

instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile

program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing

mode to specify the source operand and a second addressing mode to specify the destination address.

Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location

110

Field

V

H

N

Z

C

7

4

3

2

1

0

I

Addressing Modes

Two’s Complement Overflow Flag — The CPU sets the overflow flag when a two’s complement overflow occurs.

The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

0 No overflow

1 Overflow

Half-Carry Flag — The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during

an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded

decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C condition code bits to

automatically add a correction value to the result from a previous ADD or ADC on BCD operands to correct the

result to a valid BCD value.

0 No carry between bits 3 and 4

1 Carry between bits 3 and 4

Interrupt Mask Bit — When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts

are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set

automatically after the CPU registers are saved on the stack, but before the first instruction of the interrupt service

routine is executed.

Interrupts are not recognized at the instruction boundary after any instruction that clears I (CLI or TAP). This

ensures that the next instruction after a CLI or TAP will always be executed without the possibility of an intervening

interrupt, provided I was set.

0 Interrupts enabled

1 Interrupts disabled

Negative Flag — The CPU sets the negative flag when an arithmetic operation, logic operation, or data

manipulation produces a negative result, setting bit 7 of the result. Simply loading or storing an 8-bit or 16-bit value

causes N to be set if the most significant bit of the loaded or stored value was 1.

0 Non-negative result

1 Negative result

Zero Flag — The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation

produces a result of 0x00 or 0x0000. Simply loading or storing an 8-bit or 16-bit value causes Z to be set if the

loaded or stored value was all 0s.

0 Non-zero result

1 Zero result

Carry/Borrow Flag — The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit

7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and

branch, shift, and rotate — also clear or set the carry/borrow flag.

0 No carry out of bit 7

1 Carry out of bit 7

Table 7-1. CCR Register Field Descriptions

MC9S08AC16 Series Data Sheet, Rev. 8

Description

Freescale Semiconductor

Related parts for MC9S08AC16CFJE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: