DK-DEV-1AGX60N Altera, DK-DEV-1AGX60N Datasheet - Page 81

DK-DEV-1AGX60N

Manufacturer Part Number

DK-DEV-1AGX60N

Description

KIT DEV ARRIA GX 1AGX60N

Manufacturer

Altera

Series

Arria GXr

Type

FPGAr

Datasheet

1.EP1AGX20CF484C6N.pdf

(234 pages)

Specifications of DK-DEV-1AGX60N

Contents

Dev. Board, Quartus® II Web Edition, Reference Designs, Labs, and Complete Documentation

For Use With/related Products

1AGX60N

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

544-2372

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 81 of 234

- Download datasheet (4Mb)

Chapter 2: Arria GX Architecture

PLLs and Clock Networks

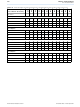

Figure 2–63. Global and Regional Clock Connections from Corner Clock Pins and Fast PLL Outputs

Note to

(1) The GCLK or RCLK in a fast PLL's quadrant can drive the fast PLL input. A dedicated clock input pin or other PLL must drive the global or regional

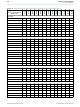

Table 2–19. Global and Regional Clock Connections from Left Side Clock Pins and Fast PLL Outputs (Part 1 of 2)

© December 2009 Altera Corporation

Clock Pins

CLK0p

CLK1p

CLK2p

CLK3p

Drivers from Internal Logic

GCLKDRV0

GCLKDRV1

GCLKDRV2

GCLKDRV3

RCLKDRV0

RCLKDRV1

RCLKDRV2

RCLKDRV3

RCLKDRV4

RCLKDRV5

RCLKDRV6

Clock Network Connectivity

Left Side Global & Regional

source. The source cannot be driven by internally generated logic before driving the fast PLL.

Figure

2–63:

PLL 7

PLL 8

Fast

Fast

v

v

v

v

—

—

—

—

—

—

—

—

—

—

—

C0

C1

C2

C3

C0

C1

C2

C3

v

v

—

—

v

v

—

—

—

—

—

—

—

—

—

RCLK0

RCLK4

v

v

v

v

—

—

—

—

—

—

—

—

—

—

—

RCLK1

RCLK5

RCLK2

RCLK6

v

v

v

v

—

—

—

—

—

—

—

—

—

—

—

RCLK3

RCLK7

v

—

—

—

—

—

—

—

v

—

—

—

v

—

—

GCLK0

v

v

v

—

—

—

—

—

—

—

—

—

—

—

—

GCLK1

v

v

v

—

—

—

—

—

—

—

—

—

—

—

—

GCLK2

—

—

—

v

—

—

—

—

—

—

—

v

—

—

—

GCLK3

v

v

v

—

—

—

—

—

—

—

—

—

—

—

—

Arria GX Device Handbook, Volume 1

v

v

v

—

—

—

—

—

—

—

—

—

—

—

—

(Note 1)

v

v

v

—

—

—

—

—

—

—

—

—

—

—

—

v

v

—

—

—

—

—

—

—

—

—

—

—

—

—

2–75

Related parts for DK-DEV-1AGX60N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT DEV ARRIA II GX FPGA 2AGX125

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

KIT DEV CYCLONE III LS EP3CLS200

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

KIT DEV STRATIX IV FPGA 4SE530

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

KIT DEV FPGA 2AGX260 W/6.375G TX

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

KIT DEV MAX V 5M570Z

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

KIT DEV STRATIX V FPGA 5SGXEA7

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

KIT DEVELOPMENT STRATIX III

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

KIT DEVELOPMENT STRATIX IV

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

KIT STARTER CYCLONE IV GX

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

KIT DEVELOPMENT STRATIX IV

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: