A000047 Arduino, A000047 Datasheet - Page 114

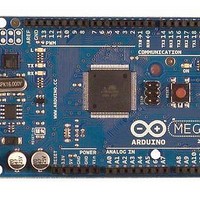

A000047

Manufacturer Part Number

A000047

Description

MCU, MPU & DSP Development Tools Mega2560

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000047

Processor To Be Evaluated

ATmega2560

Interface Type

USB, I2C, SPI

Dimensions

4 in x 2.1 in

Operating Supply Voltage

5 V

Contents

Board

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega2560

- Current page: 114 of 444

- Download datasheet (10Mb)

14.2.2

2549M–AVR–09/10

EICRB – External Interrupt Control Register B

Table 14-1.

Note:

Table 14-2.

• Bits 7:0 – ISC71, ISC70 - ISC41, ISC40: External Interrupt 7 - 4 Sense Control Bits

The External Interrupts 7 - 4 are activated by the external pins INT7:4 if the SREG I-flag and the

corresponding interrupt mask in the EIMSK is set. The level and edges on the external pins that

activate the interrupts are defined in

before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one

clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an inter-

rupt. Observe that CPU clock frequency can be lower than the XTAL frequency if the XTAL

divider is enabled. If low level interrupt is selected, the low level must be held until the comple-

tion of the currently executing instruction to generate an interrupt. If enabled, a level triggered

interrupt will generate an interrupt request as long as the pin is held low.

Table 14-3.

Note:

Bit

(0x6A)

Read/Write

Initial Value

ISCn1

ISCn1

Symbol

t

0

0

1

1

0

0

1

1

INT

1. n = 3, 2, 1or 0.

1. n = 7, 6, 5 or 4.

ISCn0

When changing the ISCn1/ISCn0 bits, the interrupt must be disabled by clearing its Interrupt

Enable bit in the EIMSK Register. Otherwise an interrupt can occur when the bits are changed.

When changing the ISCn1/ISCn0 bits, the interrupt must be disabled by clearing its Interrupt

Enable bit in the EIMSK Register. Otherwise an interrupt can occur when the bits are changed.

ISCn0

Minimum pulse width for asynchronous

0

1

0

1

0

1

0

1

Asynchronous External Interrupt Characteristics

Interrupt Sense Control

Interrupt Sense Control

ISC71

R/W

7

0

The falling edge between two samples of INTn generates an interrupt request.

The rising edge between two samples of INTn generates an interrupt request.

external interrupt

ISC70

The falling edge of INTn generates asynchronously an interrupt request.

The rising edge of INTn generates asynchronously an interrupt request.

R/W

Parameter

6

0

Any edge of INTn generates asynchronously an interrupt request.

Any logical change on INTn generates an interrupt request

ATmega640/1280/1281/2560/2561

The low level of INTn generates an interrupt request.

ISC61

The low level of INTn generates an interrupt request.

R/W

5

0

(1)

Table

(1)

ISC60

R/W

4

0

14-3. The value on the INT7:4 pins are sampled

Description

ISC51

Description

R/W

Condition

3

0

ISC50

R/W

2

0

Min

ISC41

R/W

1

0

Typ

50

ISC40

R/W

0

0

Max

EICRB

Units

ns

114

Related parts for A000047

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino