A000047 Arduino, A000047 Datasheet - Page 118

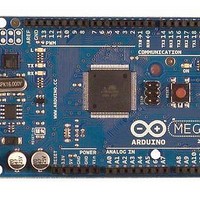

A000047

Manufacturer Part Number

A000047

Description

MCU, MPU & DSP Development Tools Mega2560

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000047

Processor To Be Evaluated

ATmega2560

Interface Type

USB, I2C, SPI

Dimensions

4 in x 2.1 in

Operating Supply Voltage

5 V

Contents

Board

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega2560

- Current page: 118 of 444

- Download datasheet (10Mb)

15. 8-bit Timer/Counter0 with PWM

15.1

15.2

15.2.1

2549M–AVR–09/10

Features

Overview

Registers

•

•

•

•

•

•

•

Timer/Counter0 is a general purpose 8-bit Timer/Counter module, with two independent Output

Compare Units, and with PWM support. It allows accurate program execution timing (event man-

agement) and wave generation.

A simplified block diagram of the 8-bit Timer/Counter is shown in

placement of I/O pins, refer to

ble I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O

Register and bit locations are listed in the

Figure 15-1. 8-bit Timer/Counter Block Diagram

The Timer/Counter (TCNT0) and Output Compare Registers (OCR0A and OCR0B) are 8-bit

registers. Interrupt request (abbreviated to Int.Req. in the figure) signals are all visible in the

Timer Interrupt Flag Register (TIFR0). All interrupts are individually masked with the Timer Inter-

rupt Mask Register (TIMSK0). TIFR0 and TIMSK0 are not shown in the figure.

The Timer/Counter can be clocked internally, via the prescaler, or by an external clock source on

the T0 pin. The Clock Select logic block controls which clock source and edge the Timer/Counter

Two Independent Output Compare Units

Double Buffered Output Compare Registers

Clear Timer on Compare Match (Auto Reload)

Glitch Free, Phase Correct Pulse Width Modulator (PWM)

Variable PWM Period

Frequency Generator

Three Independent Interrupt Sources (TOV0, OCF0A, and OCF0B)

Timer/Counter

TCCRnA

OCRnA

TCNTn

OCRnB

=

=

“TQFP-pinout ATmega640/1280/2560” on page

ATmega640/1280/1281/2560/2561

Direction

Count

Clear

Control Logic

“Register Description” on page

TOP

=

TCCRnB

Value

BOTTOM

Fixed

TOP

clk

=

Tn

0

OCnA

(Int.Req.)

OCnB

(Int.Req.)

TOVn

(Int.Req.)

Clock Select

Generation

Generation

( From Prescaler )

Waveform

Waveform

Detector

Edge

Figure

129.

15-1. For the actual

OCnA

OCnB

Tn

2. CPU accessi-

118

Related parts for A000047

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino