A000047 Arduino, A000047 Datasheet - Page 67

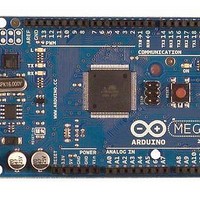

A000047

Manufacturer Part Number

A000047

Description

MCU, MPU & DSP Development Tools Mega2560

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000047

Processor To Be Evaluated

ATmega2560

Interface Type

USB, I2C, SPI

Dimensions

4 in x 2.1 in

Operating Supply Voltage

5 V

Contents

Board

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega2560

- Current page: 67 of 444

- Download datasheet (10Mb)

11.5

11.5.1

11.5.2

2549M–AVR–09/10

Register Description

MCUSR – MCU Status Register

WDTCSR – Watchdog Timer Control Register

The MCU Status Register provides information on which reset source caused an MCU reset.

• Bit 4 – JTRF: JTAG Reset Flag

This bit is set if a reset is being caused by a logic one in the JTAG Reset Register selected by

the JTAG instruction AVR_RESET. This bit is reset by a Power-on Reset, or by writing a logic

zero to the flag.

• Bit 3 – WDRF: Watchdog Reset Flag

This bit is set if a Watchdog Reset occurs. The bit is reset by a Power-on Reset, or by writing a

logic zero to the flag.

• Bit 2 – BORF: Brown-out Reset Flag

This bit is set if a Brown-out Reset occurs. The bit is reset by a Power-on Reset, or by writing a

logic zero to the flag.

• Bit 1 – EXTRF: External Reset Flag

This bit is set if an External Reset occurs. The bit is reset by a Power-on Reset, or by writing a

logic zero to the flag.

• Bit 0 – PORF: Power-on Reset Flag

This bit is set if a Power-on Reset occurs. The bit is reset only by writing a logic zero to the flag.

To make use of the Reset Flags to identify a reset condition, the user should read and then

Reset the MCUSR as early as possible in the program. If the register is cleared before another

reset occurs, the source of the reset can be found by examining the Reset Flags.

• Bit 7 - WDIF: Watchdog Interrupt Flag

This bit is set when a time-out occurs in the Watchdog Timer and the Watchdog Timer is config-

ured for interrupt. WDIF is cleared by hardware when executing the corresponding interrupt

handling vector. Alternatively, WDIF is cleared by writing a logic one to the flag. When the I-bit in

SREG and WDIE are set, the Watchdog Time-out Interrupt is executed.

Bit

0x35 (0x55)

Read/Write

Initial Value

Bit

(0x60)

Read/Write

Initial Value

WDIF

R/W

7

0

R

7

–

0

WDIE

R/W

6

0

R

6

–

0

WDP3

R/W

ATmega640/1280/1281/2560/2561

5

0

R

5

–

0

WDCE

R/W

JTRF

R/W

4

0

4

WDE

WDRF

R/W

R/W

X

3

3

See Bit Description

WDP2

R/W

BORF

R/W

2

0

2

WDP1

EXTRF

R/W

R/W

1

0

1

WDP0

R/W

PORF

0

0

R/W

0

WDTCSR

MCUSR

67

Related parts for A000047

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino