ISL6534CRZ Intersil, ISL6534CRZ Datasheet - Page 10

ISL6534CRZ

Manufacturer Part Number

ISL6534CRZ

Description

IC CTRLR PWM DUAL LINEAR 32QFN

Manufacturer

Intersil

Datasheet

1.ISL6534CVZR5229.pdf

(28 pages)

Specifications of ISL6534CRZ

Topology

Step-Down (Buck) Synchronous (2), Linear (LDO) (1)

Function

Any Function

Number Of Outputs

3

Frequency - Switching

300kHz ~ 1MHz

Voltage/current - Output 1

Controller

Voltage/current - Output 2

Controller

Voltage/current - Output 3

Controller

W/led Driver

No

W/supervisor

No

W/sequencer

Yes

Voltage - Supply

3.3 V ~ 12 V

Operating Temperature

0°C ~ 70°C

Mounting Type

*

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ISL6534CRZ

Manufacturer:

TI

Quantity:

7 155

Part Number:

ISL6534CRZ

Manufacturer:

ISL

Quantity:

20 000

Company:

Part Number:

ISL6534CRZ-T

Manufacturer:

INTERSIL

Quantity:

11 900

Part Number:

ISL6534CRZ-T

Manufacturer:

INTERSIL

Quantity:

20 000

Company:

Part Number:

ISL6534CRZR5229

Manufacturer:

Intersil

Quantity:

135

PGOOD

This digital output is an open-drain pull-down device. When

power is first applied to the IC, the output is pulled low, for

power “Not Good”. After all 3 soft-start pins complete their

ramp up with no faults (no short detected on switchers) the

power is considered “Good”, and the output pin is high-

impedance (to be pulled up to a logic high level with an

external pull-up resistor). See the PGOOD section under

Functional Description for more details.

FS/SYNC

This input allows the user to adjust the internal oscillator

used for the PWM outputs; a pull-down resistor will speed up

the oscillator; use a 0Ω resistor (or a trace) to GND to get the

default 300kHz. In addition, a digital clock signal can be fed

into this input, in order to SYNC its clock with the external

one; this allows the clock edges to line up in a way that won’t

interfere with each other.

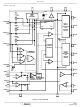

Functional Description

Overview

There are two single-phase synchronous buck converters,

and one linear regulator. Except for a common clock, the two

PWM regulators are independent. Refer to Figures 2 and 3

for a quick discussion of the circuit. The right side of the

diagram shows the 3 output stages with their components;

each switcher has an upper and lower FET, input capacitor,

bootstrap diode and capacitor, an LC output filter, and an

optional snubber.

The 3rd regulator (OUT3) is a linear, with an external NFET,

input and output capacitor. The output voltage is divided to

FB3, and compared to an internal 0.6V reference. An RC is

used for compensation.

The left side of the diagrams show the various control and

programming components. Each switcher has a compensation

network for stability that includes the output resistor divider.

VREF and REFOUT can be used as reference voltages. There

are three SS/EN pins to set the soft-start ramp of each output,

and a PGOOD output to signal when they are all done. The

FS_SYNC pin allows options for the oscillator frequency. Each

of these features will be described in more detail, either in the

Functional Description or the Application Considerations.

The first regulator (OUT1) has an internal 0.6V reference. To

set the output voltage level, connect a resistor divider

between VOUT1 and FB1.

The second regulator (OUT2) requires an external reference

connected to REFIN. For DDR memory applications

(Figure 2), connect a divide-by-two resistor divider from

VOUT1 to ground with the center point connected to REFIN.

This causes VOUT2 to track VOUT1 at one-half its value.

Connect VOUT2 to FB2 (through the compensation

resistor). A buffered copy of REFIN is provided on REFOUT.

10

ISL6534

For Independent mode operation on OUT2 (Figure 3), a 3.3V

reference is provided on VREF which can be used directly (if

VCC is high enough), or divided down for REFIN. A resistor

divider from VOUT2 to FB2 sets the output voltage.

Operational Modes

Table 1 shows how to select the various modes and phasing

between the two switching regulators.

DDR mode is chosen by connecting the SS2/EN2 pin to

VCC (5V). In this mode, SS1/EN1 is used to enable and soft-

start both OUT1 and OUT2 (a single 30µA current source is

charging a single soft-start capacitor). In addition, VOUT1

(usually divided by 2) can be used as the REFIN for OUT2.

VOUT1 is often used as VIN2 (especially when the VOUT2

current is low enough) although it is not necessary. And

OUT2 does allow both sinking and sourcing of current for the

DDR.

For Independent mode, SS2/EN2 is not connected to VCC.

Instead it is connected to a soft-start capacitor to GND,

similar to SS1/EN1. The capacitors will ramp each output

independently, and each can be turned off by pulling its

SS/EN pin to GND; releasing will start a new soft-start ramp.

SS3/EN3 is also independent of the first two. As explained

earlier, one capacitor can be shared by more than one

SS/EN pin.

To select the Phase shift between Channel 1 and 2, the

REFOUT pin is used. Tie it to the VCC pin to get 0 degrees

in either mode (which means both switchers are in phase). In

this case, the REFOUT pin is not available for use

elsewhere; the buffer is disabled. Leave REFOUT open

(driven to whatever voltage is supplied at REFIN) and it

selects 90 degrees in the DDR mode, or 180 degrees in

Independent mode; REFOUT can be used as a reference in

this case. The advantage of Phase shift is to keep the

switching current spikes from lining up to create even higher

noise, or interaction between the channels; it also reduces

the RMS current through the input capacitors, allowing fewer

caps to be employed. However, depending on the VOUT to

VIN ratios of both, there is no guarantee that opposite edges

might not line up, depending on the duty cycles; so the user

should check for that possibility.

Figure 4 shows the phases. The rising edge of LGATE1

(LG1) and LGATE2 (LG2) is fixed; the phase difference is

relative to the rising edges. The falling edge of each is the

DDR

DDR

Independent SS2 cap

Independent SS2 cap

MODE

TABLE 1. MODE AND PHASE SELECTION

EN_SS2 REFOUT

VCC

VCC

Open

Open

VCC

VCC

180 degree

90 degree

PWM1/2

0 degree

0 degree

EN1/SS1 enables

CH1 and CH2

EN1/SS1 for CH1;

EN2/SS2 for CH2

November 18, 2005

CH1/2

“

“

FN9134.2