ISL6534CRZ Intersil, ISL6534CRZ Datasheet - Page 9

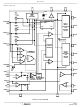

ISL6534CRZ

Manufacturer Part Number

ISL6534CRZ

Description

IC CTRLR PWM DUAL LINEAR 32QFN

Manufacturer

Intersil

Datasheet

1.ISL6534CVZR5229.pdf

(28 pages)

Specifications of ISL6534CRZ

Topology

Step-Down (Buck) Synchronous (2), Linear (LDO) (1)

Function

Any Function

Number Of Outputs

3

Frequency - Switching

300kHz ~ 1MHz

Voltage/current - Output 1

Controller

Voltage/current - Output 2

Controller

Voltage/current - Output 3

Controller

W/led Driver

No

W/supervisor

No

W/sequencer

Yes

Voltage - Supply

3.3 V ~ 12 V

Operating Temperature

0°C ~ 70°C

Mounting Type

*

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ISL6534CRZ

Manufacturer:

TI

Quantity:

7 155

Part Number:

ISL6534CRZ

Manufacturer:

ISL

Quantity:

20 000

Company:

Part Number:

ISL6534CRZ-T

Manufacturer:

INTERSIL

Quantity:

11 900

Part Number:

ISL6534CRZ-T

Manufacturer:

INTERSIL

Quantity:

20 000

Company:

Part Number:

ISL6534CRZR5229

Manufacturer:

Intersil

Quantity:

135

Pin Description

VCC

This power pin supplies bias to the control functions. It can

be connected to a nominal 5V (±5%) supply, or it can

function as a shunt regulator (nominal 5.8V), with an

external pull-up resistor (nominally 150Ω to 12V).

GND

This pin is the signal ground for the IC. The metal thermal

pad under both packages is connected to the GND potential

(through the IC substrate; the pad does NOT substitute for

the GND pin connection). But the GND pin and the metal

pad should be connected together on the board, and tied to

a good GND plane (both for electrical and thermal

conduction). The thermal pad on both packages limits metal

interconnect traces underneath the package.

VCC12 (QFN: VCC12_1, VCC12_2)

This power pin (nominal 12V) supplies the output gate

drivers, as well as some other control functions.

The QFN package has two power pins; one for each

switcher. They are electrically connected internally, but allow

for separate decoupling caps to better isolate the switching

noise, if necessary. Even if they share one capacitor, they

should both be connected externally, for lower resistance.

PGND (QFN: PGND_1, PGND_2)

This pin is the Power GND for the gate drive circuits. It is not

directly tied to GND inside the IC; it should be tied to GND

on the board.

The QFN package has two Power GNDs; one local to each

switcher; both should be connected externally to the GND

plane on the board.

SS1/EN1, SS2/EN2, SS3/EN3

These analog input pins have two functions. A 30µA current

source charges an external capacitor (to GND), to provide a

soft-start timing ramp; their respective Output voltage will

follow the ramp voltage as it powers up. The 2nd function is

Enable; when the input is left open (with the soft-start cap),

the respective output will be Enabled after the ramp reaches

the 1V level. If the input is pulled to a low logic level, the

output will be disabled.

SS2/EN2 also has a special mode function; see Table 1.

Tying it to VCC (5V) selects the DDR mode (where both

OUT1 and OUT2 share the SS1 ramp); otherwise it will be in

the Independent mode.

COMP1, COMP2

These analog output pins are used to externally compensate

the error amplifiers for their respective regulators.

FB1, FB2, FB3

These analog input pins are used to set their respective

regulator output voltages. A resistor divider from the output

9

ISL6534

to GND is compared to a reference voltage (0.6V for OUT1

and OUT3; REFIN pin for OUT2). The compensation

components also connect to these pins.

UGATE1, UGATE2

These output pins provide the gate drive for the upper

MOSFETs of OUT1 and OUT2 respectively; the voltage

comes from its bootstrap pin, typically 12V (minus the diode

drop) above the VCC12 pin.

LGATE1, LGATE2

These output pins provide the gate drive for the lower

MOSFETs of OUT1 and OUT2 respectively; the voltage

comes from VCC12.

BOOT1, BOOT2

These pins feed the bootstrap voltage (externally generated

with a diode and a capacitor) to the upper MOSFETs,

through the UGATE pins. Either BOOT pin can be connected

directly to a power supply instead (but only if the VIN voltage

of the regulator is sufficiently lower than that supply, such

that the FETs have enough gate-source voltage).

REFIN

This analog input is used as the reference voltage for OUT2

(the error amplifier compares it to the feedback resistor

divider at FB2). This voltage is also fed into a buffer, which is

output on the REFOUT pin. Note from the Electrical

Specifications Table that there is a common-mode limit for

this input; in particular, if an external 5V supply is used for

VCC, then the 3.3V from VREF should not be used directly;

it should be divided down to avoid running out of headroom.

REFOUT (VTT Buffer)

This analog output provides a buffered version of the REFIN

input, to be used by other IC’s in the system. In the DDR

mode, where VTT is generated from VDDQ, this output can

be used as a VTT Buffer.

In addition, it can be used to select the phase relationship,

but it disables the buffer in that case (see Table 1). Tying it to

VCC (5V) selects 0 degrees phase (in either mode); leaving

it open (where it can also be used as a reference output)

selects 90 degrees phase (in DDR mode) and 180 degrees

phase (in Independent Mode). A capacitor to GND is

recommended for stability (see Application Considerations).

VREF

This analog output pin is a 3.3V nominal reference, which

can be used by this IC (or others) as a voltage reference. A

capacitor to GND is recommended for stability (see

Application Considerations).

DRIVE3

This pin drives the gate of an external N-Channel MOSFET,

for OUT3, which is a linear regulator.

November 18, 2005

FN9134.2