CX28229G-14 Mindspeed Technologies, CX28229G-14 Datasheet - Page 97

CX28229G-14

Manufacturer Part Number

CX28229G-14

Description

ATM IMA 800Mbps 1.8V/3.3V 256-Pin BGA

Manufacturer

Mindspeed Technologies

Datasheet

1.CX28229G-14.pdf

(271 pages)

Specifications of CX28229G-14

Package

256BGA

Utopia Type

Level 2

Typical Operating Supply Voltage

1.8|3.3 V

Minimum Operating Supply Voltage

1.71|3 V

Maximum Operating Supply Voltage

1.89|3.6 V

Maximum Output Rate

800 Mbps

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CX28229G-14

Manufacturer:

MNDSPEED

Quantity:

16

- Current page: 97 of 271

- Download datasheet (4Mb)

CX28224/5/9 Data Sheet

6.1.2.2

28229-DSH-001-D

Interrupts

The CX2822x’s interrupt indications can be classified as either single- or dual-event;

a single-event interrupt is triggered by a status assertion; a dual-event interrupt is

triggered by either a status assertion or deassertion. Both types of interrupts are

further described in the following examples.

Single-event interrupt: When a parity error occurs on the UTOPIA transmit data bus,

an interrupt is generated on ParErrInt, bit 7, in the TXCELLINT register (0x2C). This

bit is cleared when read.

Dual-event interrupt: When LOCD occurs, bit 7 of the corresponding RXCELLINT

register (0x0D) is set to 1. This bit is cleared when the register is read. Once cell

delineation is recovered, bit 7 is set to 1 again, generating another interrupt.

All interrupt bits have a corresponding enable bit. This allows software to disable or

mask interrupts as required.

The CX2822x uses three levels of interrupt indications. The first level consists of

receive or transmit interrupt indications, which correspond to specific events on a

specific port. The second level summarizes first level interrupts and indicates framer

and one-second interrupts for each port. The third level indicates which port generated

an interrupt.

The first level interrupt indications are located in registers TXCELLINT and

RXCELLINT for each port. Each interrupt bit in these registers can be disabled in the

corresponding ENCELLR or ENCELLT register, respectively. The result is then

ORed into the appropriate bit in the port’s SUMINT register.

The second level consists of summary interrupt indications, located in the SUMINT

register. It also includes the OneSecInt and the ExInt indications. Each interrupt bit in

these registers can be disabled in the corresponding ENSUMINT register. The result

is then ORed into the appropriate bit in the SUMPORT register.

The third level contains the overall interrupt indications for each port in the

SUMPORT register. These bits can be disabled in the ENSUMPORT register. The

result is ORed to the MicroInt* pin. The MicroInt* pin can be enabled or disabled by

setting the EnIntPin (bit 3) in the MODE register (0x202).

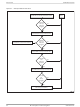

Figure 6-1

illustrates the registers involved in the interrupt generation process.

NOTE:

illustrates the flow chart of the interrupt generation process and

The IMA block does not generate interrupts.

Mindspeed Technologies

™

General Issues

Figure 6-2

6

-

3

Related parts for CX28229G-14

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

Framer SDH ATM/POS/STM-1 SONET/STS-3 3.3V 272-Pin BGA

Manufacturer:

Mindspeed Technologies

Part Number:

Description:

RS8234EBGC ATM XBR SAR

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

ATM SAR 155Mbps 3.3V ABR/CBR/GFR/UBR/VBR 388-Pin BGA

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

ATM IMA 8.192Mbps 1.8V/3.3V 484-Pin BGA

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

ATM SAR 622Mbps 3.3V ABR/CBR/GFR/UBR/VBR 456-Pin BGA

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

RS8234EBGD ATM XBR SAR, ROHS

Manufacturer:

Mindspeed Technologies

Part Number:

Description:

3-PORT T3/E3/STS-1 LIU WITH/ DJAT IC (ROHS)

Manufacturer:

Mindspeed Technologies

Part Number:

Description:

Framer SDH ATM/POS/STM-1 SONET/STS-3 3.3V 272-Pin BGA

Manufacturer:

Mindspeed Technologies

Part Number:

Description:

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

Manufacturer:

Mindspeed Technologies

Datasheet:

Part Number:

Description:

Manufacturer:

Mindspeed Technologies

Datasheet: