MC9S08DZ16 FREESCALE [Freescale Semiconductor, Inc], MC9S08DZ16 Datasheet - Page 151

MC9S08DZ16

Manufacturer Part Number

MC9S08DZ16

Description

8-Bit HCS08 Central Processor Unit (CPU)

Manufacturer

FREESCALE [Freescale Semiconductor, Inc]

Datasheet

1.MC9S08DZ16.pdf

(416 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08DZ16ACLC

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC9S08DZ16ACLF

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 151 of 416

- Download datasheet (5Mb)

8.4.3

The BDIV bits can be changed at anytime and the actual switch to the new frequency will occur

immediately.

8.4.4

The low power bit (LP) is provided to allow the FLL or PLL to be disabled and thus conserve power when

these systems are not being used. However, in some applications it may be desirable to enable the FLL or

PLL and allow it to lock for maximum accuracy before switching to an engaged mode. Do this by writing

the LP bit to 0.

8.4.5

When IRCLKEN is set the internal reference clock signal will be presented as MCGIRCLK, which can be

used as an additional clock source. The MCGIRCLK frequency can be re-targeted by trimming the period

of the internal reference clock. This can be done by writing a new value to the TRIM bits in the MCGTRM

register. Writing a larger value will decrease the MCGIRCLK frequency, and writing a smaller value to

the MCGTRM register will increase the MCGIRCLK frequency. The TRIM bits will effect the MCGOUT

frequency if the MCG is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or bypassed low

power internal (BLPI) mode. The TRIM and FTRIM value is initialized by POR but is not affected by other

resets.

Until MCGIRCLK is trimmed, programming low reference divider (RDIV) factors may result in

MCGOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock

timing specifications (see the

If IREFSTEN and IRCLKEN bits are both set, the internal reference clock will keep running during stop

mode in order to provide a fast recovery upon exiting stop.

8.4.6

The MCG module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz

in FEE and FBE modes, 1 MHz to 16 MHz in PEE and PBE modes, and 0 to 40 MHz in BLPE mode.

When ERCLKEN is set, the external reference clock signal will be presented as MCGERCLK, which can

be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by

the FLL or PLL and will only be used as MCGERCLK. In these modes, the frequency can be equal to the

maximum frequency the chip-level timing specifications will support (see the

If EREFSTEN and ERCLKEN bits are both set or the MCG is in FEE, FBE, PEE, PBE or BLPE mode,

the external reference clock will keep running during stop mode in order to provide a fast recovery upon

exiting stop.

If CME bit is written to 1, the clock monitor is enabled. If the external reference falls below a certain

frequency (f

bit in the System Reset Status (SRS) register will be set to indicate the error.

Freescale Semiconductor

Bus Frequency Divider

Low Power Bit Usage

Internal Reference Clock

External Reference Clock

loc_high

or f

loc_low

depending on the RANGE bit in the MCGC2), the MCU will reset. The LOC

Device Overview

MC9S08DZ60 Series Data Sheet, Rev. 4

chapter).

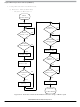

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

Device Overview

chapter).

151

Related parts for MC9S08DZ16

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: